Компьютерная грамотность с Надеждой

Компьютерная грамотность предполагает наличие представления о пяти поколениях ЭВМ, которое Вы получите после ознакомления с данной статьей.

Когда говорят о поколениях, то в первую очередь говорят об историческом портрете электронно-вычислительных машин (ЭВМ).

Фотографии в фотоальбоме по истечении определенного срока показывают, как изменился во времени один и тот же человек. Точно так же поколения ЭВМ представляют серию портретов вычислительной техники на разных этапах ее развития.

Всю историю развития электронно-вычислительной техники принято делить на поколения. Смены поколений чаще всего были связаны со сменой элементной базы ЭВМ, с прогрессом электронной техники. Это всегда приводило к росту быстродействия и увеличению объема памяти. Кроме этого, как правило, происходили изменения в архитектуре ЭВМ, расширялся круг задач, решаемых на ЭВМ, менялся способ взаимодействия между пользователем и компьютером.

|

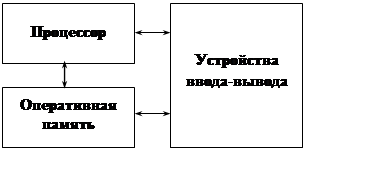

Структурная схема компьютера.

Процессор – устройство, выполняющее все вычисления, а также выполняющее управление последовательностью вычислений.

Оперативная память – место для хранения данных, используя которые, процессор может выполнять вычисления.

Устройства ввода-вывода предназначены:

1. для ввода данных (например: клавиатура, «мышь», сканер);

2. для вывода данных (например: видеомонитор, принтер);

3. для обмена данными (например: накопители на жестких и гибких дисках, накопители на магнитной ленте, модемы).

Данные могут быть выведены на носители данных, после вывода могут храниться на носителях данных (жестких и гибких дисках, магнитной ленте, Flash-накопителях) и затем эти данные могут быть введены с этих носителей.

Элементная база бытовой электроники

Как уже было сказано выше, локомотивом развития элементной базы электроники стал быстро растущий, развивающийся рынок ПК. Благодаря этому современная бытовая техника напоминает специализированный компьютер. Телевизоры, домашние кинотеатры, проигрыватели DVD дисков имеют такие эксплуатационные параметры, которые лет двадцать назад просто невозможно было представить.

Даже стиральные машины, холодильники, простые новогодние гирлянды управляются микроконтроллерами. Современные поющие и говорящие детские игрушки, сделанные в Китае, также с микроконтроллерным управлением. Кстати, поразительный факт: еще в шестидесятые годы двадцатого столетия китайцы не могли наладить даже выпуск детекторных приемников, а теперь почти вся электроника делается в Китае.

В промышленности также любое современное устройство управления техпроцессом, даже не очень сложное построено на основе микроконтроллеров и, как правило, имеет интерфейс для подключения к ПК. Такой интерфейс имеют, например, электронные счетчики электроэнергии, что позволяет использовать их в системах автоматического учета.

Надежность современных электронных компонентов достаточно высока. Тем не менее, нередки случаи, когда любая электронная техника приходит в негодность, нуждается в ремонте. В случае поломки бытовой электронной техники не всегда возможно отнести неисправное устройство в специализированную мастерскую, просто не везде они есть. Тогда на помощь приходят радиолюбители, ремонтирующие технику в своих домашних мастерских.

Квалификация таких домашних мастеров, как правило, очень высокая, ведь ремонтируется весьма широкий спектр электронной техники: от простых дверных звонков до спутниковых систем телевидения. Об устройстве и организации таких мастерских на дому будет рассказано в следующей статье.

Л05_Элементная база ЭВМ.doc

Элементная база ЭВМ

1. Классификация элементов и узлов ЭВМ

2. Комбинационные схемы

3. Схемы с памятью

4. Проблемы развития элементной базы

1. Классификация элементов и узлов ЭВМ

Как правило, в структуре ЭВМ выделяют следующие структурные единицы: ● элементы, ● узлы, ● блоки и ● устройства.

1. Нижний уровень обработки реализуют элементы. Каждый элемент предназначается для обработки единичных электрических сигналов, соответствующих битам информации. Такая детализация соответствует вполне определенным операциям преобразования информации, заложенным в программах пользователей.

2. Узлы обеспечивают одновременную обработку группы сигналов — информационных слов.

3. Блоки реализуют некоторую последовательность в обработке информационных слов — функционально обособленную часть машинных операций (блок выборки команд, блок записи-чтения и др.).

4. Устройства предназначаются для выполнения отдельных машинных операций и их последовательностей.

Все современные вычислительные машины строятся на комплексах (системах) интегральных микросхем (ИС). Схема называется интегральной, если ее компоненты и соединения между ними выполнены в едином технологическом цикле, на едином основании и имеют общую герметизацию и защиту от механических воздействий.

Функционально микросхемы могут соответствовать устройству, узлу или блоку, но каждая из них состоит из комбинации простейших логических элементов, реализующих функции формирования, преобразования, запоминания сигналов и т.д.

Элементы ЭВМ можно классифицировать по различным признакам (типу сигналов, назначению элементов, технология их изготовления и т.д.).

1. Применяют два способа физического представления сигналов: импульсный и потенциальный. При импульсном способе представления сигналов единичному значению некоторой двоичной переменной ставится в соответствие наличие импульса (тока или напряжения), нулевому значению — отсутствие импульса (рис. 1, а).

При потенциальном или статическом представлении сигналов единичное значение двоичной переменной отображается высоким уровнем напряжения, а нулевое значение — низким уровнем (рис. 1. б).

Рис. 1. Представление информации в ЭВМ: а — импульсные сигналы; б — потенциальные сигналы

Различают последовательный и параллельный коды передачи и представления информации в ЭВМ.

При последовательном коде представления данных используются одиночные шины или линии передачи. Обработка такой информации производится последовательно.

Параллельный код предполагает параллельную и одновременную фиксацию всех разрядов данных на различных шинах. Это дает возможность ускорить обработку во времени, но затраты на аппаратурные средства при этом возрастают.

Во всех ЭВМ используются и параллельно-последовательные коды.

При этом информация отображается частями. Части поступают на обработку последовательно, а каждая часть данных представляется параллельным кодом.

- формирующие,

- логические и

- запоминающие.

● Простейшие логические элементы преобразуют входные сигналы в соответствии с элементарными логическими функциями. Сложные преобразования могут приводить к построению многоуровневых схем, которые представляет композицию простейших.

● Запоминающим элементом называется элемент, который способен принимать и хранить код двоичной цифры.

2. Комбин ационные схемы

Обработка входной информации в выходную обеспечивается преобразователями или цифровыми автоматами двух видов: комбинационными схемами и схемами с памятью.

Комбинационные схемы (КС) — это схемы, у которых выходные сигналы Y = (у1, у2,. уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х= (х1, х2, . хп), поступающих в тот же момент.

Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу же при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида У = f(X).

Логические функции и их комбинационные схемы подразделяют на регулярные и нерегулярные структуры.

Регулярные структуры предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими.

^ В нерегулярных структурах такое построение отсутствует.

Из регулярных наиболее распространены шифраторы/дешифраторы, схемы сравнения, комбинационные сумматоры, коммутаторы. Рассмотрим принципы их построения.

1. Дешифраторы (ДШ — DC) — это комбинационные схемы с n входами и m = 2 n выходами. Дешифраторы широко используются в ЭВМ для выбора информации по определенному адресу, для расшифровки кода операции и др. Единичный сигнал, формирующийся на одном из m выходов, однозначно соответствует некоторой комбинации входных сигналов.

Например, разработка структуры дешифратора (ДШ— DC) для трех входов n=3 позволяет получить таблицу истинности и логические зависимости.

(m = 2 3 = 8 выходов):

| На рис. 2 представлены структурная схема ДШ, построенная в базисе (И, НЕ), и ее условное обозначение на принципиальных электрических схемах ЭВМ. Кружочки у линий, выходящих из логических элементов, указывают на инверсию функций, реализуемых элементами. |  |

|

Рис. 2. Структурная схема ДШ (а) и его обозначение на принципиальных электрических схемах (б)

^ Таблица 1 Таблица истинности дешифратора на рис. 2

| Входы | Выходы | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| x1 | x2 | x3 | y0 | y1 | . | y5 | . | y7 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 0 | 0 | 0 | 1 | 0 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Входы | Выходы | ||||||||

| x1 | x2 | x3 | x4 | x5 | x6 | x7 | y0 | y1 | y2 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

3. Схемы сравнения, или компараторы, обычно строятся как поразрядные. Они широко используются и автономно, и в составе более сложных схем, например при построении сумматоров. Пусть логическая зависимость варианта некоторого компаратора:

^ Таблица истинности (табл. 3) отражает логику работы i—го разряда схемы сравнения при сравнении векторов А и В (выход равен 1 только тогда, когда значения входов равны друг другу). На рис. 4 а показана структурная схема компаратора.

^ Таблица 3 Таблица истинности компаратора

| Входы | Выходы | |

| ai | bi | Y На выходе 1, если входы равны между собой i |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

На рис. 4 показана структурная схема компаратора, где помимо выхода Y2, фиксирующего равенство значений разрядов, показаны выходы Y1 и Y3. соответствующие сигналам «больше» и «меньше».

а а |

б б |

^ Рис. 4. Структурная схема (а) и обозначение компаратора на электрических схемах (б)

4. Комбинационный полусумматор. Принципы его построения и работы вытекают из правил сложения двоичных цифр. При сложении одноразрядных двоичных цифр можно выявить закономерности в построении и многоразрядных сумматоров.

Сначала рассмотрим сумматор, обеспечивающий сложение 2-х двоичных цифр аi и Ьi, считая, что переносы из предыдущего разряда не поступают. Этой логике отвечает сложение младших разрядов двоичных чисел. Процесс сложения описывается таблицей истинности (табл. 4) и логическими зависимостями логики работы самого младшего разряда любого сумматора ,где Si — функция одноразрядной суммы и Pi — функция формирования переноса. Перенос формируется, когда ai=1 и bi=1.

^ Таблица 4 Таблица истинности комбинационного полусумматора

| Входы | Выходы | ||

| ai | bi | Si | Pi |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Логические зависимости имеют следующие зависимости:

Здесь как SM – обозначена приведенная выше схема одноразрядного сумматора.

3. Схемы с памятью

Передача значения Q между моментами времени t и (t+1) осуществляется обычно с применением двухступенчатой памяти и синхронизирующих импульсов (СИ).

Пример 1. Автомат памяти — триггер имеет вход R (Reset — сброс) для установки элемента в «нулевое состояние» и вход S (Set — : установка) — для установки в «единичное» состояние. При отсутствии сигналов (т.е. R=S=0) элемент должен сохранять свое состояние до тех пор, пока не будут получены новые сигналы на входе R или S.

Условия работы триггера могут быть показаны в виде таблицы переходов, представляющей собой модификацию таблицы истинности. Наиболее простой вид таблицы переходов представлен в табл. 5 (ниже).

^ Таблица 5 Условия работы триггера

| Входы | Состояния q | |||

| R | S | qt | qt+1 | Режим |

| 0 | 0 | 0/1 | 0/1 | Хранение |

| 1 | 0 | 0/1 | 0 | Установка 0 |

| 0 | 1 | 1/0 | 1 | Установка 1 |

| 1 | 1 | ? | ? | Запрещенное состояние |

^ Таблица расшифровывается так. Элемент памяти может сохранять значение qt=0 или qt=1 в зависимости от ранее установленного состояния. При отсутствии входных сигналов на входах R и S (R=0 и S=0) значения qt+1 в первой строке таблицы в точности повторяют значения qt. При поступлении сигнала R=1 (установки «нуля») элемент независимо от своего состояния принимает значение, равное нулю, qt+1=0. Если же на вход S поступает сигнал установки «единицы» (S=1), то qt+1=1 независимо от предыдущего состояния qt. Одновременное поступление сигналов на входы R и S запрещено, т.к. может привести к непредсказуемому состоянию. В схемах формирования R и S должны быть блокировки, исключающие их совпадения, S=R=1.

Для таблицы переходов 5 может быть построена т.н. диаграмма Вейча (табл. 6).

Таблица 6 ^ Диаграмма Вейча для таблицы переходов триггера

В этой таблице знаком « » отмечены запрещенные комбинации входных сигналов. Эти комбинации могут быть использованы для упрощения логических зависимостей.

Логическая зависимость, описывающая работу элемента памяти, имеет вид:

Добавление в него комбинаций, соответствующих запрещенным ситуациям и помеченных знаком « », т.е.

позволяет еще больше упростить уравнение триггера

Для реализации полученной зависимости в базисе И-НЕ применим правило де Моргана и получим итоговую функцию

По данной зависимости можно построить схему асинхронного RS-триггера. В ней следует соединить выход qt+1 со входом qt (рис.9) – см. штриховую линию.

а а |

б б |

в в |

Рис. 9. Схема асинхронного RS-триггера: а — схема; б — обозначение на принципиальных электрических схемах; в — временная диаграмма

- R(Reset — сброс) — вход установки триггера в нулевое состояние, q=0;

- S(Set — установка) — вход установки триггера в единичное состояние, q=1;

- Т(Toggle — релаксатор) — счетный вход триггера;

- J(Jerk — внезапное включение) — вход установки JK-триггера в единичное состояние, q=1;

- К(Kill — внезапное выключение) — q=0.

Дополнение этого триггера комбинационными схемами синхронизации на входе и выходе позволяет получить триггеры с более сложной логикой работы: синхронные RS, T-, JK-, D-триггеры и целый ряд комбинированных RST-, JKRS-, DRS- триггеров.

Двухкаскадная схема RS-триггера (рис. 10, в) нашла наиболее широкое применение для построения n -разрядных схем запоминания — всевозможных регистровых схем.

На рис.11 приведена схема Т-триггера или, триггера со счетным входом.

При значении входа Xt=0 — триггер сохраняет свое ранее установленное состояние — режим хранения состояния,

Регистром называется узел, предназначенный для приема, временного хранения и выдачи машинного слова. Регистры могут также использоваться для некоторых операций преобразования данных: для сдвига кода числа (слова) на определенное число разрядов влево или вправо, для преобразования последовательного кода числа в параллельный и наоборот и т.д. Эти дополнительные функции регистров обеспечиваются путем усложнения схем хранения, выбора более сложных триггеров и подключения дополнительных логических схем на их входах и выходах. Т.о. регистры представляют собой совокупность триггеров, число которых соответствует числу разрядов в слове, и вспомогательных схем, обеспечивающих выполнение различных операций над словом.

На рис. 14 показана функциональная схема n -разрядного регистра, построенного на RS-триггерах. Информация в регистр записывается под действием сигнала «Запись».

а а |

б б |

Рис. 14. Схема регистра на RS-триггерах: а — функциональная схема; б — условное обозначение регистра

Счетчик — это узел ЭВМ, позволяющий осуществлять подсчет поступающих на его вход сигналов и фиксацию результата в виде многоразрядного двоичного числа. Счетчик, состоящий из n -триггеров, позволяет подсчитывать до N = 2 n .

В ЭВМ счетчики используются для подсчета импульсов, сдвигов, формирования адресов и т.д. Функционально различают суммирующие, вычитающие, реверсивные счетчики. Они также отличаются друг от друга логикой работы дополнительных логических элементов, подключаемых к триггерам. В основу построения любого счетчика положено свойство Т-триггеров изменять свое состояние при подаче очередного сигнала на счетный вход Т.

Сумматор — это узел ЭВМ, в котором суммируются коды чисел. Любой сумматор это комбинация одноразрядных сумматоров. Сумматоры различают по принципам построения: накапливающего и комбинационного типа. Сумматоры накапливающего типа строят на сложных JKRS-триггерах, дополняя их выходы схемами формирования и распространения переносов. Процесс сложения при этом осуществляется поэтапно. Сначала на триггерах сумматора фиксируется код первого операнда, затем на счетные коды разрядов подается код второго операнда. На каждом триггере формируются одноразрядные суммы и значения переносов между разрядами. Для построения сумматоров чаще применяют сумматоры комбинационного типа. У них на входе и выходе имеются регистры для хранения и преобразования кодов операндов и результата (рис. 15).

Рис. 15. Упрощенная схема сумматора ЭВМ

Регистр Рг1 предназначается для хранения кода 1-го операнда, а Рг2 —2-го. Сумматор по сигналам из устройства управления (УУ) настраивается на выполнение машинной операции, соответствующей коду операции, находящемуся в коде команды. Результат операции фиксируется в РгЗ. Он может использоваться для продолжения вычислений. Для этого предусматривается возможность перезаписи содержимого регистра РгЗ на Рг1 в качестве значения одного из операндов при выполнении очередной операции.

4. Проблемы развития элементной базы (ЭБ)

Одним из главных факторов достижения высокого быстродействия и производительности ЭВМ — построение их на новейшей элементной базе. Смена поколений ЭВМ в значительной степени связана с переходами на новые поколения ЭБ, достижения новых частотных диапазонов работы схем в рамках доступных технологий. Успехи в создании новой ЭБ определяются передовыми научными и техническими достижениями целого ряда наук (физики, химии, оптики, механики).

Все современные ЭВМ строятся на микропроцессорных наборах, основу которых составляют большие (БИС) и сверхбольшие интегральные схемы (СБИС). Технологический принцип производства интегральных схем заключается в послойном изготовлении их частей по циклу «программа — рисунок — схема».

На напыленный фоторезисторный слой наносится рисунок будущего слоя микросхемы. Затем рисунок протравливается, фиксируется, закрепляется и изолируется от новых слоев. На основе этого создается пространственная твердотельная структура. Так, СБИС типа Pentium включает несколько миллионов транзисторов, размещаемых в многослойной структуре.

Степень микроминиатюризации, размер кристалла ИС, производительность и стоимость определяются типом литографии. До настоящего времени доминировала оптическая литография, когда рисунки наносятся световым лучом. Ведущие компании производят кристаллы размером ~400 мм 2 — для процессоров и ~200 мм 2 — для схем памяти. Размер — от 0,1 мкм (толщина волоса ~ 100 мкм) и меньше.

Дальнейшие успехи связываются с электронной, ионной и рентгеновской литографией. Это позволило выйти на размеры 90; 65 и даже 45 нм. Вместо алюминиевых проводников в микросхемах применяют медные соединения, что повышает частоту работы схем.

Высокие технологии имеют ряд проблем (высокую чистоту материалов, вакуумные установки и снижение рабочих температур и пр.).

В настоящее время основой построения всех микросхем была и остается КМОП-технология (со структурой «металл — окисел — полупроводник»).

Так как микросхемы СБИС не могут работать с высокой тактовой частотой, то в ЭВМ будущих поколений их целесообразно комплексировать в системы. При этом несколько СБИС должны работать параллельно, а слияние работ в системе должно обеспечивать сверхскоростные ИС (ССИС), которые не могут иметь высокую степень интеграции.

Большие исследования проводятся также в области использования явления сверхпроводимости. Работа микросхем при температурах, близких к абсолютному нулю, позволяет достигнуть максимальных частот при отсутствии рассеиваемой энергии.

Внедрение новых технологий производства микропроцессоров испытывает и экономические проблемы. Например, строительство нового завода по производству микросхем обходится в несколько млрд. долл. Это заставляет искать новые альтернативные пути построения будущих ЭВМ. Интенсивные поиски идут по многим направлениям.

- создание молекулярных и биокомпьютеров (нейрокомпьютеров);

- разработку квантовых компьютеров;

- разработку оптических компьютеров.

Во многих странах проводятся опыты по синтезу молекул на основе их стереохимического генетического кода, способных менять ориентацию и реагировать, на воздействия током, светом и т.п. Например, ученые Hewlett—Packard и Калифорнийского университета доказали принципиальную возможность создания молекулярной памяти ЭВМ на основе молекул роксана. Продолжаются работы по созданию логических схем, узлов и блоков. По оценкам ученых, подобный компьютер в 100 млрд. раз будет экономичнее современных микропроцессоров.

- параллельность обработки информа-ционных потоков;

- способность к обучению и настройке;

- способность к автоматической классификации;

- более высокую надежность;

- ассоциативность.

В настоящее время уже созданы и используются программные нейропакеты, которые доказывают возможность построения подобных машин на СБИС.

Принцип работы элементов квантового компьютера основан на способности электрона в атоме иметь различные уровни энергии. Переход электрона с нижнего энергетического уровня на более высокий связан с поглощением кванта электромагнитной энергии — фотона. При излучении фотона осуществляется обратный переход. Всеми подобными переходами можно управлять, используя действие электромагнитного поля от атомного или молекулярного генератора. Этим исключаются спонтанные переходы с одного уровня на другой.

Основным строительным блоком квантового компьютера служит Quantum Bit, который может иметь большое число состояний. Для таких блоков определен логически полный набор элементарных функций. Есть эксперименты по созданию RISC-процессора на RSFQ-логике (Rapid Single Flux Quantum) и проекты таких ЭВМ.

Идея построения оптического компьютера давно разрабатывается. Многие устройства ЭВМ используют оптику в своем составе: сканеры, дисплеи, лазерные принтеры, оптические диски CD-ROM и DVD-ROM. Появились и успешно работают оптоволоконные линии связи. Остается создать устройство обработки информации с использованием световых потоков. Способность света параллельно распространяться в пространстве дает возможность создавать параллельные устройства обработки. Это позволило бы на много порядков ускорить быстродействие ЭВМ.

Пока отсутствуют проекты создания чисто оптических процессоров, но уже проводятся эксперименты по проектированию оптоэлектронных и оптонейронных устройств.

Каковы же состояние и прогноз развития микропроцессоров в настоящее время?

Основные конкуренты по производству интегральных разрядных микросхем фирмы ^ Intel и AMD преодолели рубеж 3,5 ГГц.

В ближайшем будущем основной путь – многоядерные процессоры, но следует ожидать выхода микропроцессора до 5 ГГц.

Таким образом, можно сделать вывод, что в настоящее время возможности микроэлектроники еще не исчерпаны.

detector