Как работает процессор?

Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Арифметико-логическое устройство: классификация, устройство и принцип действия

АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ подразделяются на три основные категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление. ). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ. ). Операции над битами обычно подразумевают сдвиги.

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части :

а) микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

б) операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке 1. В состав АЛУ входят регистры Рг1 — Рг7, в которых обрабатывается информация , поступающая из оперативной или пассивной памяти N1, N2, . NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма , которая записывается в виде последовательности микрокоманд A1,A2, . Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2. Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2. рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, . уs, в ОЗУ. Функции регистров, входящих в АЛУ:

Рг1 — сумматор (или сумматоры) — основной регистр АЛУ, в котором образуется результат вычислений;

Рг2, РгЗ — регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции);

Рг4 — адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата;

Ргб — k индексных регистров, содержимое которых используется для формирования адресов;

Рг7 — i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся : сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе . Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования «операция/ режим адресации» базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

3. Перспективные направления развития компьютеров

Мир современных компьютеров необычайно разнообразен. Кроме микропроцессоров, встраиваемых во всевозможные устройства, и разных типов персональных компьютеров существуют значительно более мощные вычислительные системы.

Это серверы в глобальной компьютерной сети, управляющие её работой и хранящие огромные объёмы информации.

Это многопроцессорные системы параллельной обработки данных, обеспечивающие:

• сокращение времени решения вычислительно сложных задач;

• сокращение времени обработки больших объёмов данных;

• решение задач реального времени;

• создание систем высокой надёжности.

Время однопроцессорных вычислительных систем прошло. Не только суперкомпьютеры, но и современные персональные компьютеры, ноутбуки, игровые приставки основаны на многопроцессорных, многоядерных и других технологиях, предполагающих одновременное выполнение множества инструкций.

В наши дни электронная техника уже подошла к предельным значениям своих технических характеристик, которые определяются физическими законами. Поэтому идёт поиск неэлектронных средств хранения и обработки данных, ведутся работы по созданию квантовых и биологических компьютеров, проводятся исследования в области нанотехнологий.

Логические схемы

Логическая схема — это набор объединенных вентилей с входными и выходными сигналами. На рис 1.1 тоже изображена схема у которой входными сигналами являются A и B, выходной сигнал идет от операции ИЛИ; также у нее есть три вентиля: два И, один ИЛИ. Теперь давайте рассмотрим некоторые виды схем с которыми нам потребуется встречаться в дальнейшем, к ним относятся: комбинационные, арифметические, интегральные схемы.

Комбинационные схемы

Комбинационная схема — это схема с одним дополнительным свойством: значения выходных сигналов зависят только от входных, или другими словами, в ней нет никаких запоминающих устройств. Из этого вида схем создаются переиспользуемые компоненты, которые применяются для реализации большинства других схем, мы рассмотрим несколько, а именно: компаратор, декодер, мультиплексор/демультиплексор.

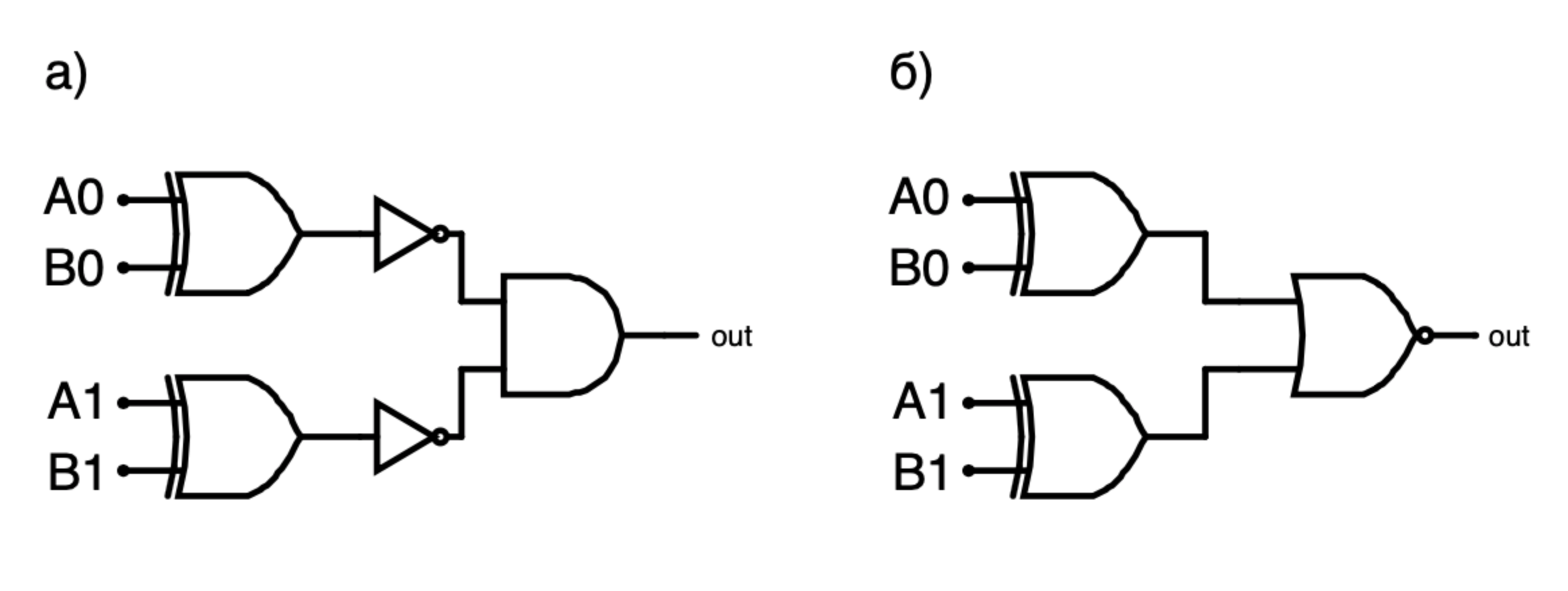

Компаратор имеет n входных парных линий (то есть 2n входов) и одну выходную линию. Логика его работы заключается в том, чтобы сравнить каждую пару битов (биты слова A сравниваются с соответствующими битами слова B) и при неравенстве хоть одной из них выдать 0 (если за ложь принят 0), иначе 1. Давайте построим таблицу истинности (табл. 1.1) для однобитного компаратора; можно заметить, что она равна таблице истинности ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (когда к операции добавлен НЕ, то все выходные значения в таблице становятся противоположными). Теперь давайте расширим его до двухбитного компаратора, построим таблицу истинности (табл. 1.2) для него от двух переменных значения которых зависит от двух однобитных компаратора, то есть от двух ИСКЛЮЧАЮЩЕГО ИЛИ-НЕ; в ней значение 1 в CMP0 (и CMP1) значит, что два входа какото-то компаратора равны, 0 наоборот, то есть 1 в столбце R должна быть только, когда значения равны в двух компараторах. Эта таблица истинности совпадает с таблицей И, то есть мы объединяем все ИСКЛЮЧАЮЩЕГО ИЛИ-НЕ операцией И и у нас получится двухбитный компаратор (рис. 1.3а). Для дальнейшего расширение компаратора необходимо лишь добавить ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и подсоединить его к И. Недостаток такой реализации заключается в ее избыточности, нам требуется добавлять вентили НЕ для каждого ИСКЛЮЧАЮЩЕГО ИЛИ; мы можем от этого избавится (рис. 1.3б), если заменим вентиль И с НЕ входами на ИЛИ-НЕ, так как их таблицы истинности совпадают.

Таблица. 1.1. Таблица истинности для однобитного компаратора.

| A | B | CMP |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| CMP0 | CMP1 | R |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Рисунок 1.3. Две схемы двухбитных компараторов.

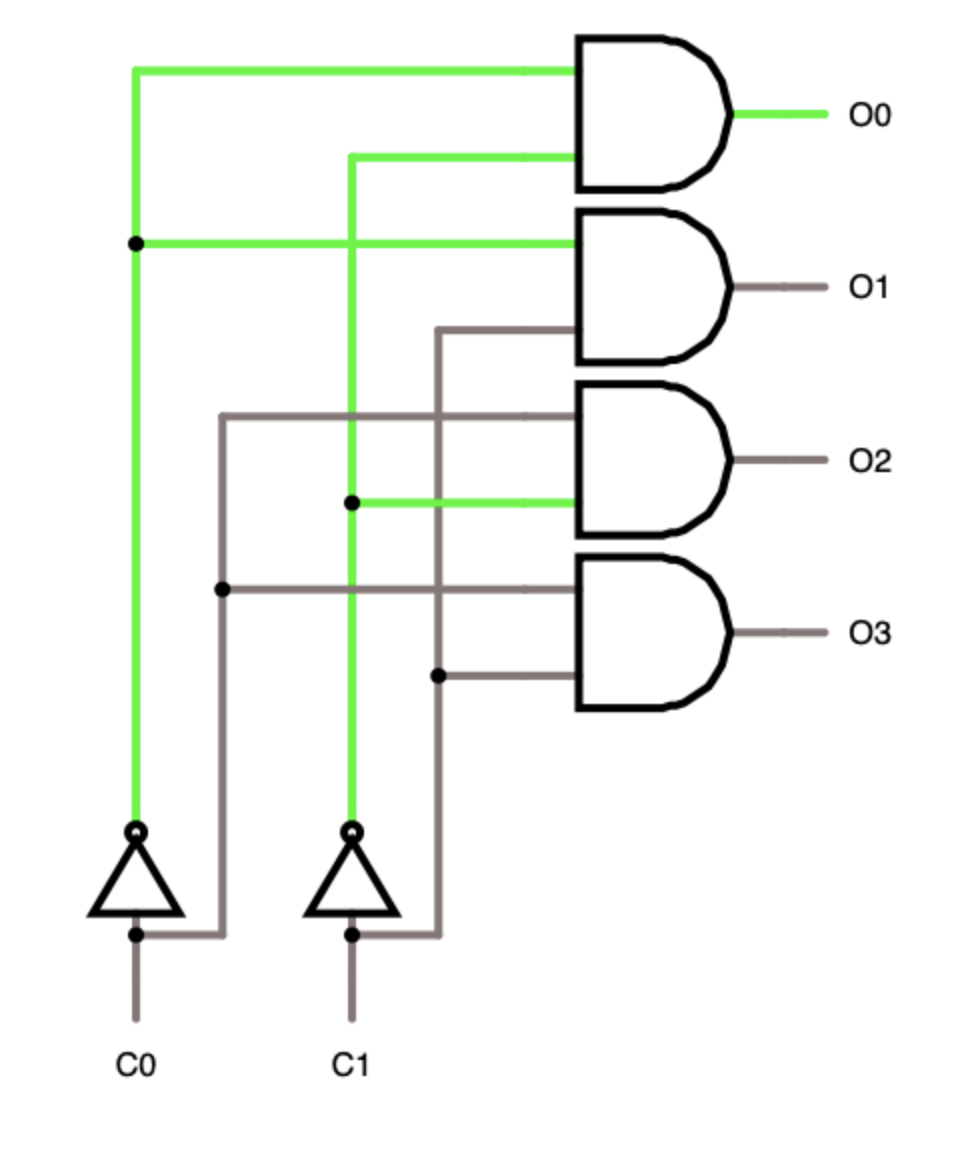

Декодер обладает n входными линиями, 2^n выходными, он реализован так, чтобы сигнал (истинна, 1) прошел только в одну выходную линию. Каждый выходной вентиль И получает свою комбинацию значений переменных, которые (значения) находятся в какой-то строке таблицы истинности, а как мы уже знаем, строку таблицы истинности можно реализовать как минтерму, то есть мы каждую строку представляем как вентиль И (рис. 1.4) от нескольких переменных. Основное применение декодера заключается в выборочном включении разных частей схемы (или схем), например, у АЛУ (о нем далее) имеется несколько операции, которые он может выполнять над входными значениями, чтобы их выбрать одну из них используется декодер.

Рисунок 1.4 Декодер.

Мультиплексор/демультиплексор

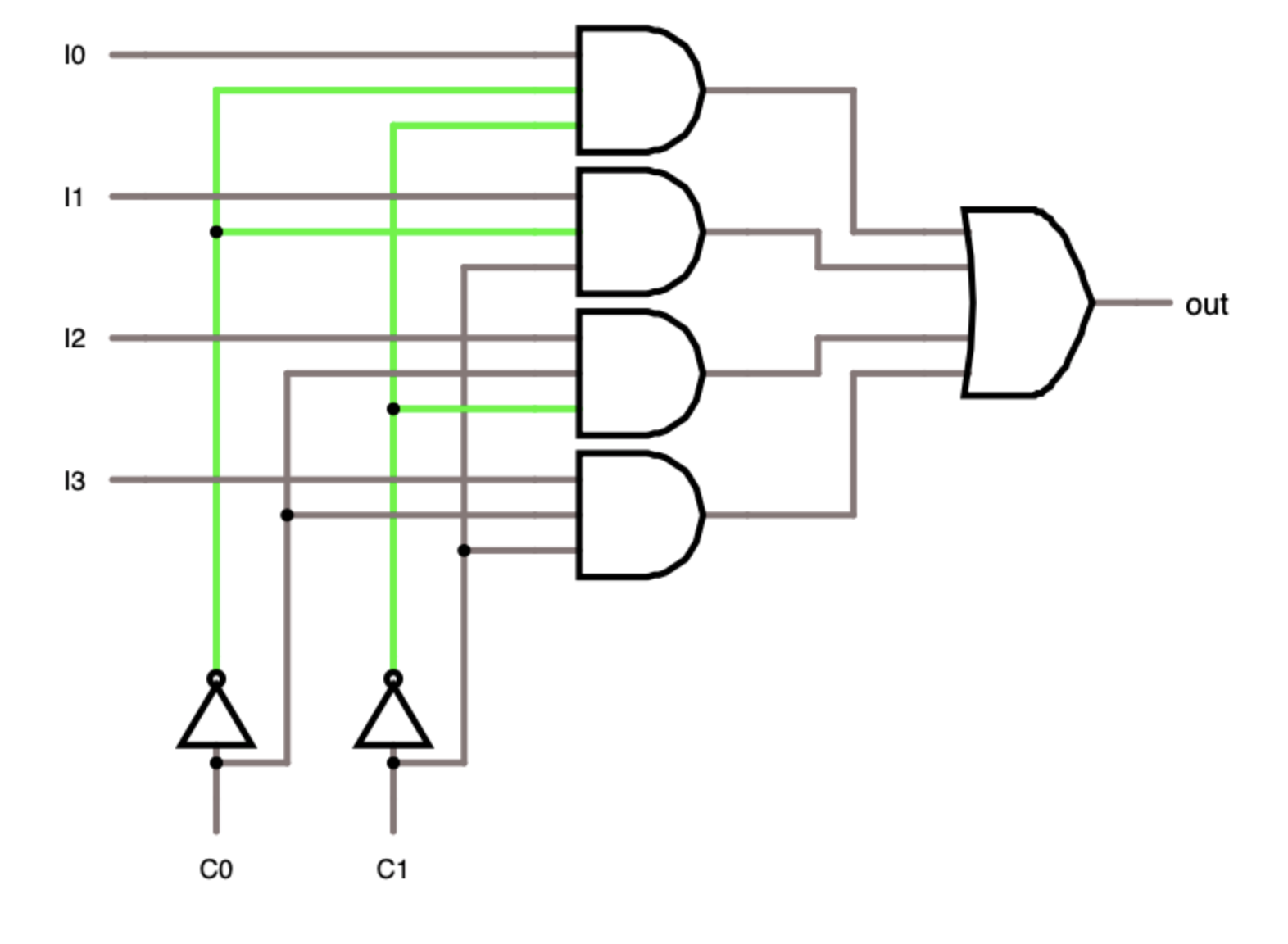

Мультиплексор обладает 2^n входными линиями, n линиями управления и одной выходной линией. Он в реализации в какой-то степени похож (рис 1.5) на декодер, если представить входы декодера как линии управления, дополнить каждый вентиль И дополнительным входным сигналом и объединить выходные значения всех И одним ИЛИ. Суть его работы заключается в том, чтобы на выход поступал сигнал только от одной из возможных входных линий. Мультиплексор применяется в разных целях, например, он может пригодиться для преобразования параллельного кода в последовательный. Допустим у нас есть параллельная (это значит, что линии работают одновременно) шина с несколькими линиями по которым параллельно передаются биты; чтобы считать нужное нам слово (обычно разрядность слова соответствует разрядности регистра в процессоре) мы соединяем линий шины с входами мультиплексора и последовательно включаем по одному входу, допустим сверху вниз, тем самым на выход у нас пойдет точная последовательность битов.

Демультиплексор является обратным мультиплексору, он имеет одну входную линию, n линий управления и 2^n выходных линий. Логика его работы точно такая же как и в мультиплексоре, только один входной сигнал идет в один из выходных. Может быть использован для преобразования последовательного кода в параллельный.

Рисунок 1.5. Мультиплексор.

Арифметические схема

Данный вид схем выполняет арифметические операции над входными сигналами. Основными схемами являются: логические функции, сумматор, схема сдвига, АЛУ (ALU, Arithmetic Logic Unit).

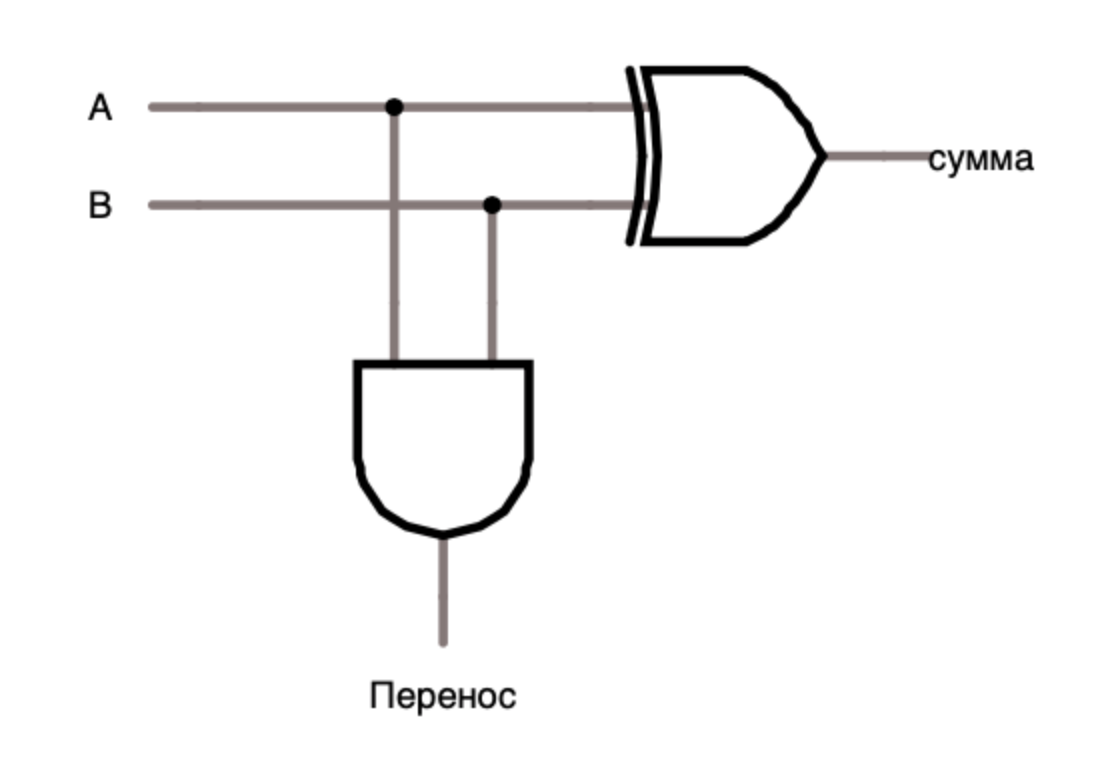

Полусумматор и полный сумматор

Полусумматор состоит из двух входных и двух выходных линий, Полусумматор является простой схемой (рис. 1.6) из двух вентилей: И и ИСКЛЮЧАЮЩЕЕ ИЛИ. Сам по себе полусумматор может складывать только одноразрядные значения, но зачем же тогда нам нужен полный сумматор? В основном мы хотим складывать значения с большей разрядностью, но только одним полусумматором мы удовлетворить это желание не может. Когда мы складываем два одноразрядных значения, то у нас может произойти переполнение (табл. 1.3 последняя строка истинности в столбике перенос). Это когда результат операции не помещается в той разрядности, которой обладают входные элементы (в данном случае 1). При сложении двух единиц получает двойка, которую нельзя сохранить в одном бите, поэтому необходимо перенести его, чтобы воспользоваться при дальнейших вычислениях, но так как в полусумматоре не предусмотрена возможность использования двух значений и переноса одновременно, то складывать значения с разрядностью более чем единицу не получится. Например, допустим мы складываем два 3-разрядных числа, 5 (101 в двоичной) и 7 (111 в двоичной), сложение двух чисел начинается с младших разрядов, на входы полусумматора направляются 1 и 1, на выходе суммы получаем 0 и на выходе переноса 1, вот здесь и возникает проблема, следующие значения, которые должны пойти в полусумматор, это 0 и 1 соответственно, но, что делать с переносом, ведь для него нет никакого свободного входа, а отбросить его нельзя, поэтому полусумматоры не могут напрямую использоваться для сложений.

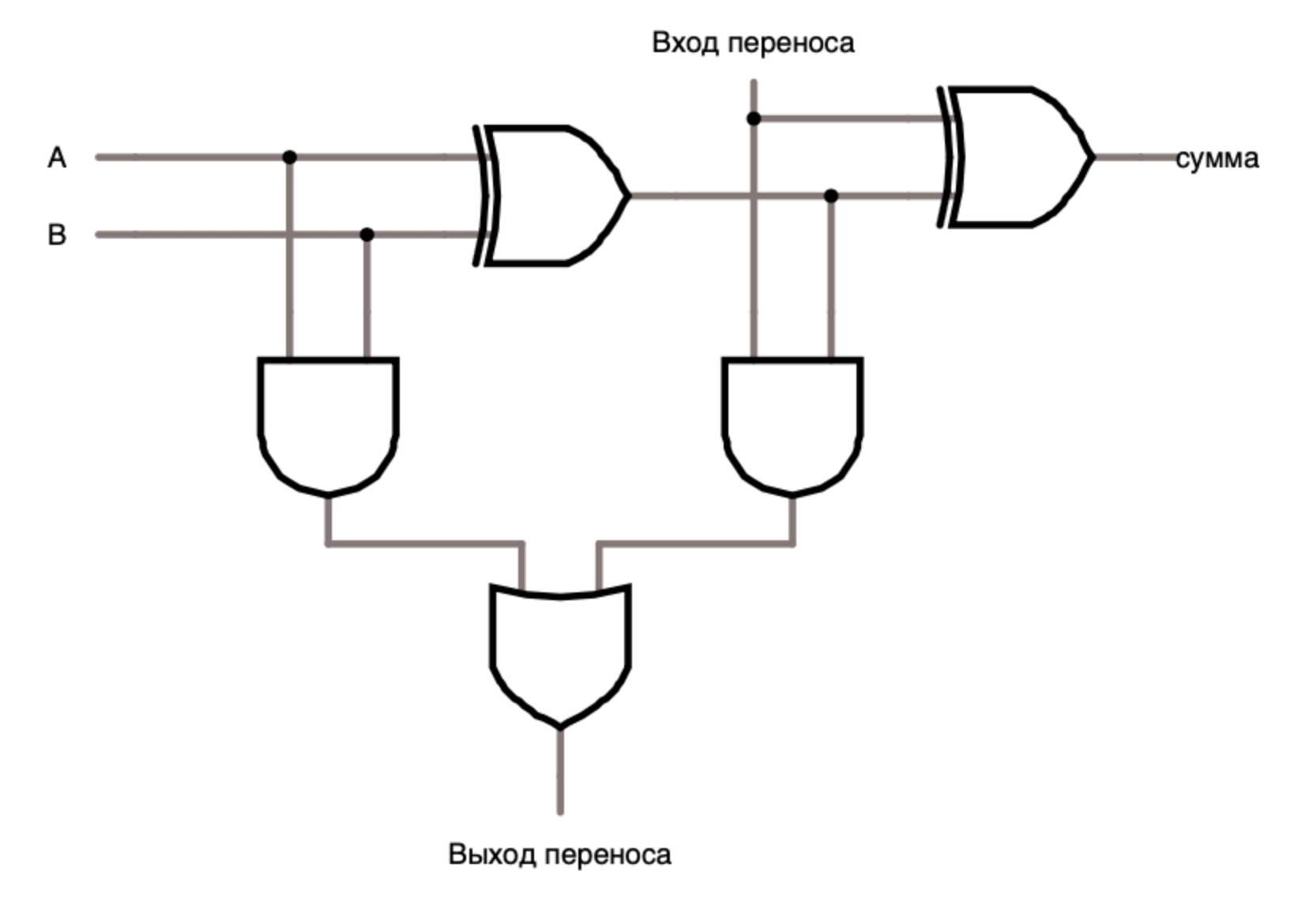

У полного сумматора есть (рис. 1.7) три входных линии и две выходные линии. Входной перенос, как и выходной, используется для возможности объединения сумматоров в один с большей разрядностью. Сумматор состоит из двух полусумматоров, чтобы построить сумматор большей разрядности, необходимо только объединить сумматоры через входные и выходные переносы.

Рисунок 1.6. Схема полусумматор.

Таблица 1.3. Таблица истинности полусумматора.

| A | B | Сумма | Перенос |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Рисунок 1.7. Схема полного сумматора.

Таблица 1.4. Таблица истинности полного сумматора.

| A | B | Вход перенос | Сумма | Выход перенос |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Схема сдвига

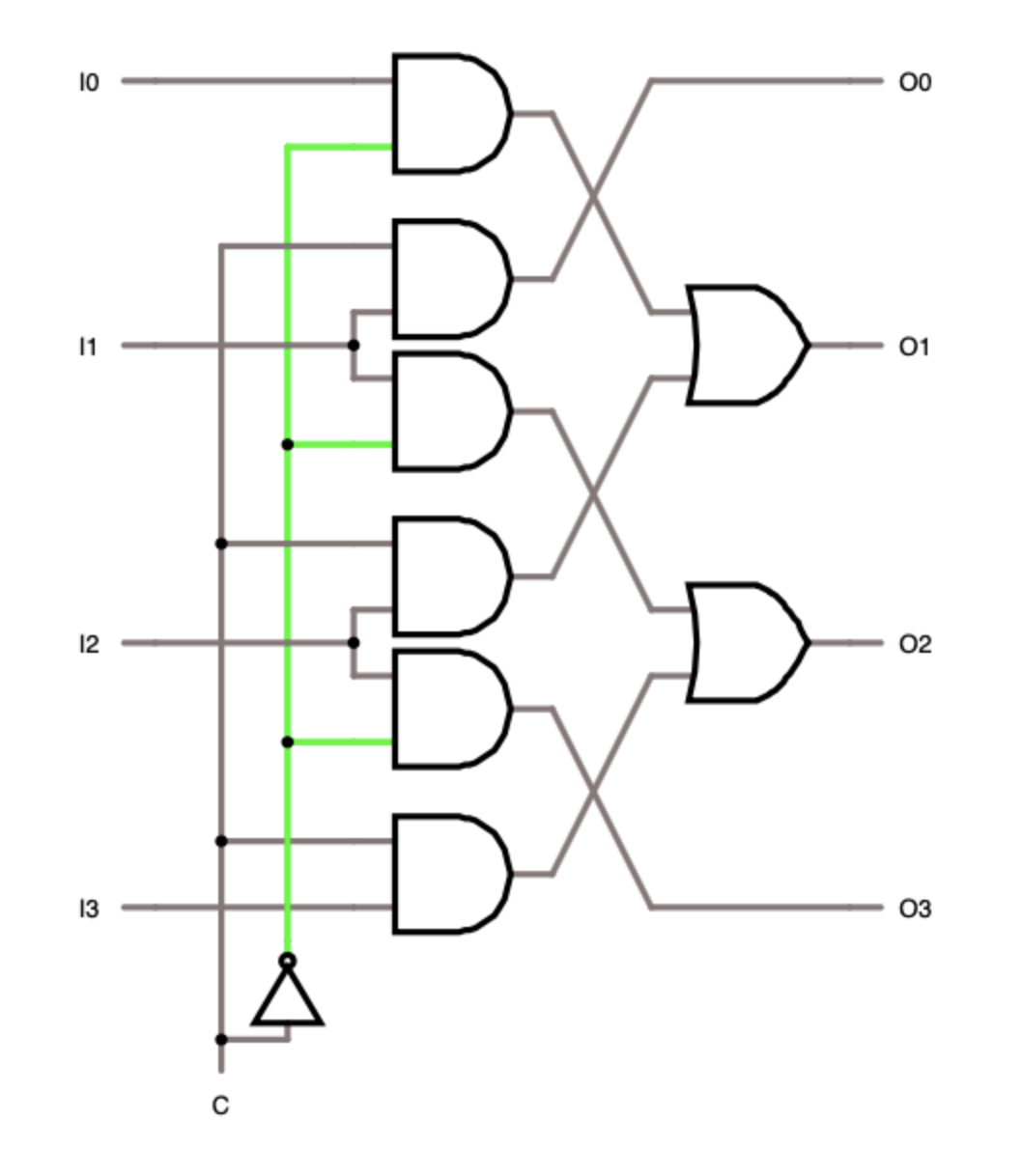

Сдвиг необходим для того, чтобы, например, выполнять умножение (сдвиг влево) и деление (сдвиг вправо), но только с числами, которые являются степенью двойки (1, 2, 4, 8 и тд). Схема сдвига (рис. 1.8) должна выполнять смещение на одну позицию влево или вправо в зависимости от бита направления. Бит направления (С) в зависимости от своего значения включает те или иные вентили И. Если он равен 0 (сдвиг влево), то сигнал который идет напрямую (то есть не проходит через НЕ) будет выключать вентиль который находятся выше в паре из двух вентилей И и один крайний вентиль И снизу. Сигнал, который проходит через НЕ, будет включать нижние вентиль в паре из двух вентилей И и один крайний вентиль И сверху. Это значит, что входные значения In будут выходить только из вентилей И выходные сигналы, которых направлены в нижнюю сторону; старший бит (I3) будет утерян, так как самый нижний вентиль И не пропустит входной сигнал дальше. Аналогичная ситуация происходит, когда бит направления равен 1 (сдвиг вправо), только теперь будут включены другие вентили И и сигнал уже будет направлен в противоположную (в данной реализации) сторону, и, следовательно, произойдет сдвиг вправо.

Рисунок 1.8. Схема сдвига.

Арифметико Логическое Устройство

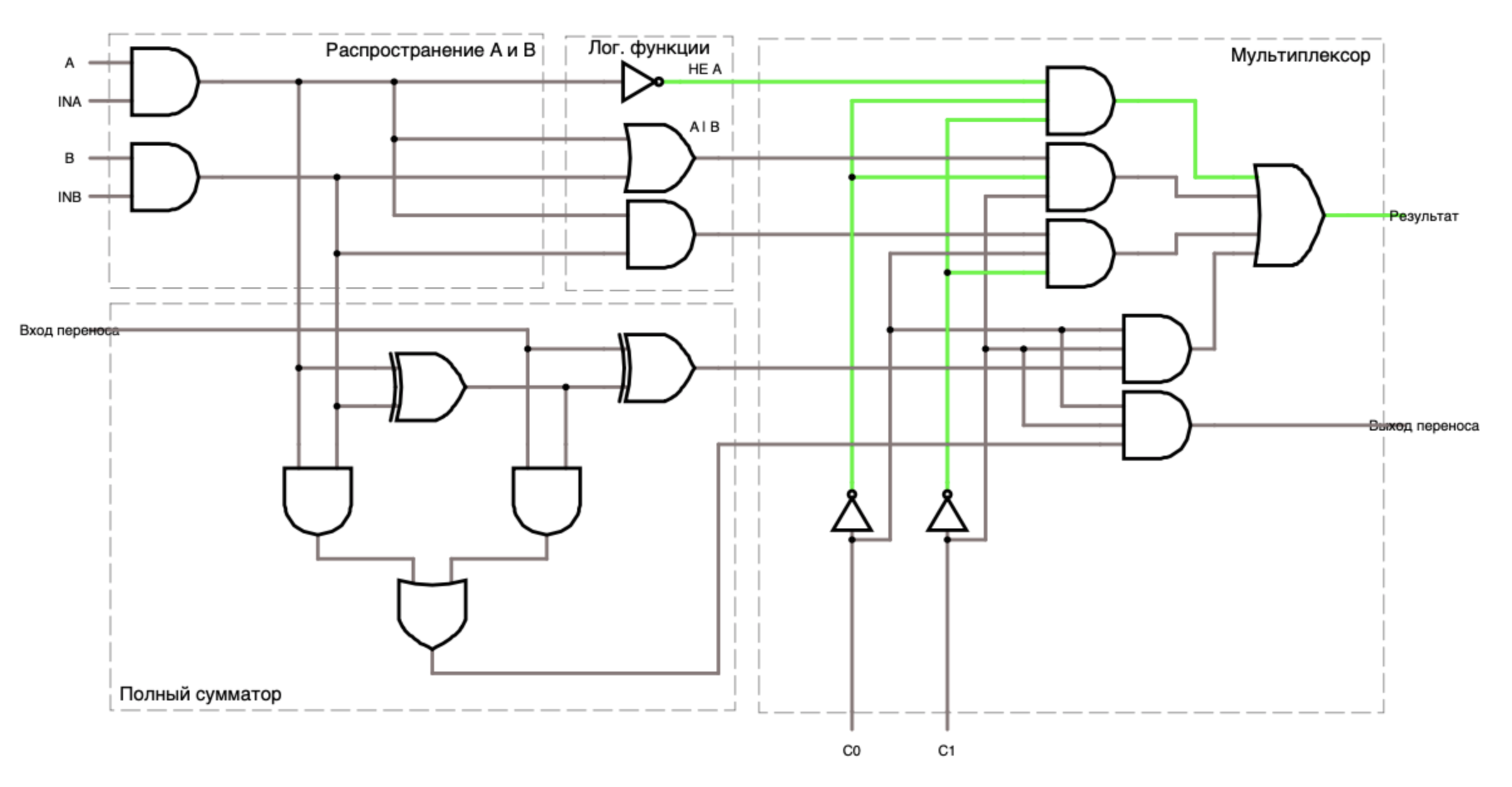

АЛУ — это схема (рис. 1.9), которая содержит в себе множество арифметических схем, она предназначена для того, чтобы в одном месте хранить все операции необходимые для какой-либо цели. Реализация АЛУ разделяется на несколько частей (в данной реализации): распространение входных операндов, логические функции, сумматор и мультиплексор. Как мы помним декодер должен выполнять«включение» операций, но здесь я решил сделать мультиплексор, который подает на выход «Результат» значение, только одной из четырех операций; два нижних вентиля И в нем делят одну и ту же комбинацию при которой мультиплексор работает, это необходимо потому, что «Выход переноса» и «Сумма» сумматора являются частью одной операции, то есть оба этих входа должны работать только когда выбрано суммирование. Наш АЛУ предназначен для работы с одноразрядными значениями, но его можно почти без проблем изменить на большую разрядность. Входные линии INA и INB предназначены для включения/выключения A и B соответственно.

Рисунок 1.9. Схема АЛУ.

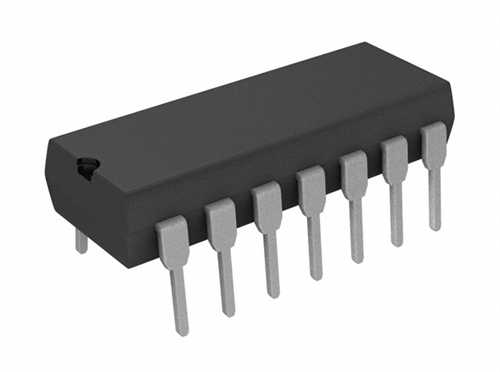

Интегральные схемы

Также известна как микросхема, это те же схемы показанные выше, только они помещены в корпус, который определяет, то где должны находится выводы для сигналов. Этот вид схем возник из-за того, что продавать отдельные схемы и вентили не очень целесообразно: по крайне мере из-за того, что нет стандарта, который бы говорил как, где и в каком кол-ве должны располагаться входные и выходные сигналы.

Есть куча разных видов корпусов, но мы рассмотрим наиболее известные:

- Dual Inline Package (DIP) представляет собой корпус (рис. 2.0а) у которого выводы (входные и выходные сигналы) расположены с двух сторон параллельных друг другу, кол-во выводов в данном корпусе варьируется в пределах от 14 до 68 (только четное кол-во). Данный корпус используется при небольших и/или дешевых схемах.

- Pin Grid Array (PGA) обладает выводами со всех четырех сторон (рис. 2.0б).

- Land Grid Array (LGA) обладает выводами в виде контактов по всей (зависит от стандарта) площадке (нижняя часть) корпуса. LGA (рис. 2.0в) обладает одним важным преимуществом перед другими корпусами: большое кол-во выводов, что особенно важно для таких микросхем как процессоры.

Содержание

Разработчик компьютера ENIAC, Джон фон Нейман, был первым создателем АЛУ. В 1945 году он опубликовал первые научные работы по новому компьютеру, названному EDVAC (Electronic Discrete Variable Computer). Годом позже он работал со своими коллегами над разработкой компьютера для Принстонского института новейших исследований (IAS). Архитектура этого компьютера позже стала прототипом архитектур большинства последующих компьютеров. В своих работах фон Нейман указывал устройства, которые, как он считал, должны присутствовать в компьютерах. Среди этих устройств присутствовало и АЛУ. Фон Нейман отмечал, что АЛУ необходимо для компьютера, поскольку оно гарантирует, что компьютер будет способен выполнять базовые математические операции включая сложение, вычитание, умножение и деление

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части :

- микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

- операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

Рисунок 1 — Структурная схема арифметико-логического устройства

Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке 1. В состав АЛУ входят регистры Рг1 — Рг7, в которых обрабатывается информация , поступающая из оперативной или пассивной памяти N1, N2, . NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма , которая записывается в виде последовательности микрокоманд A1,A2, . Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2. Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2. рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, . уs, в ОЗУ. Функции регистров, входящих в АЛУ:

- Рг1 — сумматор (или сумматоры) — основной регистр АЛУ, в котором образуется результат вычислений;

- Рг2, РгЗ — регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции);

- Рг4 — адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата;

- Ргб — k индексных регистров, содержимое которых используется для формирования адресов;

- Рг7 — i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся : сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе. Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования «операция/ режим адресации» базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.