Булева алгебра. часть 3. контактные схемы

Этот закон непосредственно следует из приведенных выше выражений аксиом алгебры логики (таблицы истинности логических

элементов). Верхние два выражения могут быть полезны при построении коммутаторов, ведь подавая на один из входов элемента

«2И» логический ноль или единицу можно либо пропускать сигнал на выход, либо формировать на выходе нулевой потенциал.

Второй вариант использования этих выражений заключается в возможности избирательного обнуления определённых разрядов

многоразрядного числа. При поразрядном применении операции «И» можно либо оставлять прежнее значение разряда, либо

обнулять его, подавая на соответствующие разряды единичный или нулевой потенциал. Например, в восьмиразрядном двоичном

числе требуется обнулить 6, 3 и 1 разряды. Тогда, при выполнении операции поразрядного логического умножения получим:

В приведенном примере отчетливо видно, что для обнуления необходимых разрядов в маске (нижнее число) на месте соответствующих

разрядов записаны нули (не забываем, что счет начинается с нулевого разряда), в остальных разрядах записаны единицы. В исходном

числе (верхнее число) на месте 6 и 1 разрядов находятся единицы. После выполнения операции «И» на этих местах появляются нули.

На месте третьего разряда в исходном числе находится ноль. В результирующем числе на этом месте тоже присутствует ноль.

Остальные разряды исходного числа, как и требовалось по условию задачи, не изменены.

Записывать логические единицы в нужные нам разряды многоразрядного двоичного числа можно точно таким же образом. В этом

случае необходимо воспользоваться нижними двумя выражениями закона одинарных элементов. При поразрядном применении операции

«ИЛИ» можно либо оставлять прежнее значение разряда, либо заносить в него единичное значение, подавая на соответствующие

разряды нулевой или единичный потенциал. Пусть требуется записать единицы в 7 и 6 биты восьмиразрядного числа.

Тогда, при выполнении операции поразрядного логического суммирования исходного числа с маской устанавливаемых бит, получим:

История науки и техники Com New

Сложные цифровые логические устройства, входящие в состав компьютера, состоят из ряда элементарных логических элементов, построенных на базе средств электронной техники. При производстве этих электронных логических элементов используют различные технологии и схемотехнические решения, такие как: ДТЛ (диодно-транзисторная логика), ТТЛ (транзисторно-транзисторная логика), ЭСЛ (эмиттерно-связанная логика), технологии, основанные на использовании полевых транзисторов, и т. д. Логические элементы позволяют реализовать любую логическую функцию. Входные и выходные сигналы логических элементов, соответствующие двум логическим состояниям 1 и 0, могут иметь один из двух установленных уровней электрического напряжения, который зависит от схемотехнического решения логического элемента. Например, для логических элементов, основанных на технологии ТТЛ, высокий уровень электрического напряжения (2,4 ? 5 В) соответствует значению логической единицы (истина), а низкий уровень (0 ? 0,4 В) – логическому нулю (ложь).

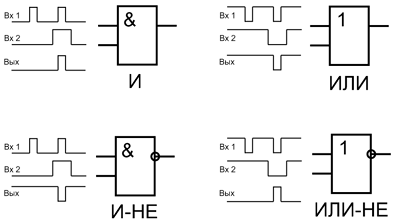

Три приведенных ниже логических элемента составляют функционально полную систему для проектирования цифровых логических устройств, в том числе и соответствующих логических блоков и устройств компьютера, поскольку реализуют функционально полный набор логических функций, состоящий из логических функций: И (конъюнкции), ИЛИ (дизъюнкции), НЕ (отрицания).

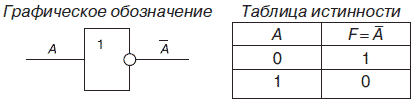

1. Логический элемент НЕ, который называется также инвертором, выполняет логическую операцию отрицания (инверсии).

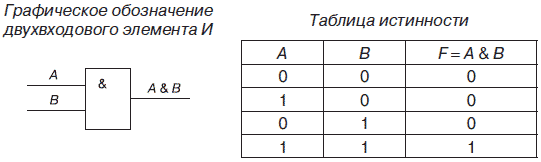

2. Логический элемент И, называемый также конъюнктором, выполняет операцию логического умножения (конъюнкции), теоретически может иметь бесконечное число входов, на практике ограничиваются числом входов от двух до восьми.

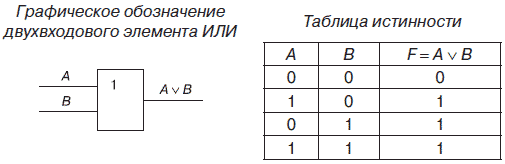

3. Логический элемент ИЛИ, называемый также дизъюнктором, выполняет операцию логического сложения (дизъюнкции), теоретически может иметь бесконечное число входов, на практике ограничиваются числом входов от двух до восьми.

При проектировании цифровых логических устройств часто возникает задача по заданной таблице истинности записать выражение для логической функции и реализовать ее в виде логической схемы, состоящей из функционально полного набора логических элементов. Данную задачу называют также задачей синтеза логических схем или логических устройств.

Синтез логических схем на основе функционально полного набора логических элементов состоит из представления логических функций, описывающих данные логические схемы в нормальных формах. Нормальной формой представления считается форма, полученная посредством суперпозиций вспомогательных логических функций – минтермов и макстернов.

Минтермом называют логическую функцию, которая принимает значение логической единицы только при одном значении логических переменных и значение логического нуля при других значениях логических переменных. Например, минтермами являются логические функции F, F, F и F (см. рис. 4.3).

Макстерном называют логическую функцию, которая принимает значение логического нуля только при одном значении логических переменных и значение логической единицы при других значениях логических переменных. Например, макстернами являются логические функции F, F, F и F (см. рис. 4.3).

Из минтермов и макстернов методом суперпозиции можно составить логические функции, которые называются соответственно логической функцией, представленной посредством совершенных дизъюнктивных нормальных форм (СДНФ), и логической функцией, представленной посредством совершенных конъюнктивных нормальных форм (СКНФ). Полученные таким образом функции СДНФ и СКНФ будут представлять искомую логическую функцию по заданной таблице истинности. После получения функций СДНФ и СКНФ их необходимо преобразовать (минимизировать). Преобразование данных функций с целью их минимизации осуществляется с помощью законов алгебры логики и специальных разработанных методов: метод Квайна, карты Карно, диаграммы Вейча и т. д.

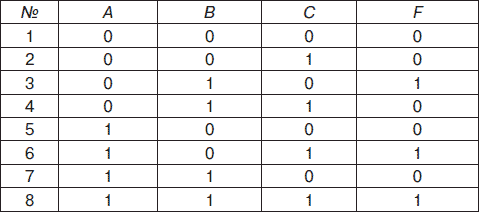

Рассмотрим задачу синтеза на примере модифицированной таблицы истинности, приведенной на рис. 4.6. Для данной таблицы истинности необходимо записать выражение для выходной функции F, провести ее преобразование (минимизацию) на основе законов алгебры логики и, используя основные логические элементы – НЕ, И и ИЛИ, разработать логическую схему реализации выходной функции F.

Рис. 4.6. Таблица истинности логических переменных A, В и С

Значения логических переменных А, В и С и соответствующие значения функции F приведены в таблице истинности (см. рис. 4.6), где в столбце № – указан номер комбинации логических переменных A, В и С.

Для решения указанной задачи представим логическую функцию F в виде СДНФ, а затем и в СКНФ. Найдем вспомогательные функции минтермы и макстермы. В заданной таблице истинности выходная функция F принимает логическое значение, равное логической единице, при комбинациях логических переменных A, В и С, указанных под номерами 3, 6, 8, а значение, равное логическому нулю – при комбинациях, указанных под номерами 1, 2, 4, 5,7.

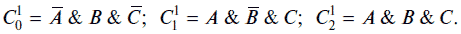

Минтермы запишем в следующем виде:

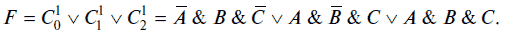

Минтермы представляют собой логические произведения (конъюнкции) логических переменных А, В, и С при значениях логической функции F, равных логической единице (комбинации 3, 6, 8). Сомножители (логические переменные A, В и С) входят в минтерм в прямом виде (без отрицания), если их значения равны логической единице, и в инверсном (с отрицанием), если их значения равны логическому нулю. Логическая функция F в СДНФ будет равна логической сумме минтермов:

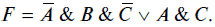

После минимизации логической функции Fc использованием законов алгебры логики получим ее искомое выражение:

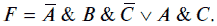

Макстермы запишем в следующем виде:

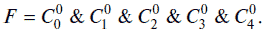

Макстермы представляют собой логические суммы (дизъюнкции) логических переменных А, В, и С при значениях логической функции F, равных логическому нулю (комбинации 1, 2, 4, 5, 7). Слагаемые (логические переменные A, В, и С) входят в макстерм в прямом виде (без отрицания), если их значения равны логическому нулю, и в инверсном (с отрицанием), если их значения равны логической единице. Логическая функция F в СКНФ будет равна логическому произведению макстермов:

Поскольку полученное выражение для F в виде СКНФ является более громоздким по сравнению с представлением F в виде СДНФ, то в качестве окончательного выражения для F примем ее выражение в виде СДНФ, т. е.

Аналогичным образом можно получить выражение для любой логической функции, которая представлена с помощью заданной таблицы истинности с Означениями логических переменных.

Используем полученное выражение логической функции F для разработки (построения) логической схемы на основе функционально полного набора логических элементов НЕ, И и ИЛИ. При построении логической схемы необходимо учитывать установленные в алгебре логики правила (приоритеты) для выполнения логических операций, которые в данном случае реализуются с помощью логических элементов НЕ, И и ИЛИ. Порядок производимых логических операций будет следующий: операция инверсии (отрицания), операция логического умножения (конъюнкции) и затем операция логического сложения (дизъюнкции). Реализация функции F в виде логической схемы, приведена на рис. 4.7.

Рис. 4.7. Реализация функции F в виде логической схемы

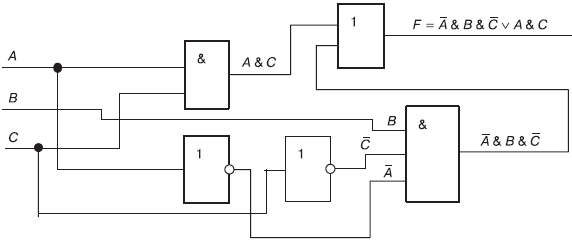

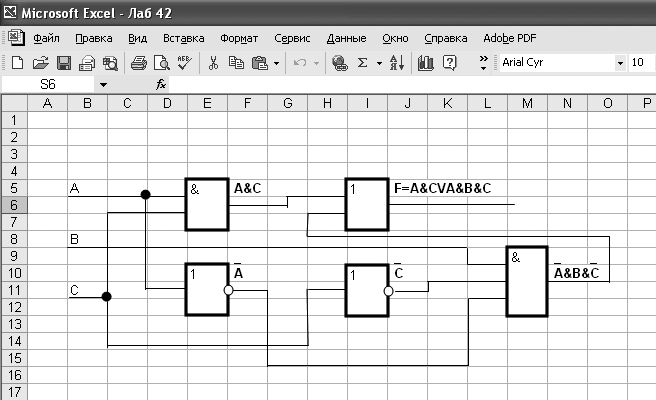

Для графического отображения логических схем существуют различные компьютерные программы, называемые графическими редакторами. Данные программы могут быть включены в другие компьютерные программы, например в программах Microsoft Word и Microsoft Excel такие редакторы реализованы с помощью панелей инструментов «Рисование», или быть самостоятельными программами, например Paint, Microsoft Visio и т. д. Воспользуемся встроенным графическим редактором (панель «Рисование») программы MS Excel для графического отображения логической схемы функции F. Данная логическая схема показана на рис. 4.8.

Рис. 4.8. Графическое отображение логической функции F с помощью программы MS Excel

На основе функционально полного набора логических элементов построены различные электронные устройства, входящие в состав компьютера. К таким устройствам относятся сумматоры (выполняющие операции сложения двоичных чисел), триггеры (устройства, имеющие два устойчивых состояния: логического нуля и логической единицы и используемые в качестве двоичных элементов памяти), регистры памяти (состоящие из набора триггеров), двоичные счетчики, селекторы (переключатели сигналов), шифраторы, дешифраторы и т. д.

Рассмотренные выше таблицы истинности логических элементов показывают установившиеся значения логических переменных. Однако когда логические переменные представлены в виде электрических сигналов, то необходимо некоторое время для того, чтобы значение логической функции достигло уровня установившегося состояния из-за внутренних задержек по времени в электронных логических элементах. В среднем задержка электрического сигнала такого элемента составляет 10 с. В компьютере двоичные сигналы проходят через множество электронных схем, и задержка по времени может стать значительной. В этом случае выделяется отрезок времени (такт) на каждый шаг логической операции. Если операция заканчивается раньше, чем заканчивается тактовое время, то устройство, входящее в состав компьютера, ожидает ее окончания. В результате скорость выполнения операций несколько снижается, но достигается высокая надежность, так как обеспечивается синхронизация между многими параллельно выполняющимися операциями в компьютере. Синхронизация устройств в компьютере обеспечивается с помощью специального генератора – генератора тактовой частоты, который вырабатывает электрические импульсы стабильной частоты.

Логические операции

Логические операции Для создания объектов более сложных, чем изначальные звезды, прямоугольники и эллипсы, мы можем использовать логические операции. Это гораздо проще, чем полноценная векторная графика, где мы будем создавать фигуры с нуля.Для выполнения логических

Логические И и ИЛИ Вы уже видели, что такое управляющие структуры и как их использовать. Для решения тех же задач есть еще два способа. Это логическое И — «&&» и логическое «ИЛИ» — « || ». Логическое И используется следующим образом:выражение_1&&выражение_2Сначала

Логические схемы

Логические схемы необходимы для реализации функций алгебры логики в цифровом устройстве. Для составления логических схем используются логические вентили (элементарные логические схемы), реализующие логические операции. Упомянутые базисы позволяют сократить перечень логических вентилей, хотя и стремление к полной минимизации этого перечня путем использования наименьших базисов не совсем практично. Мы рассмотрим логические вентили упомянутого базиса

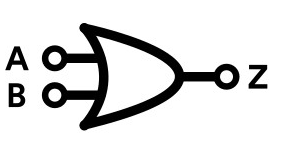

Логические вентиль И

У логического вентиля И два входа (А, В) и один выход (Z). Вентиль можно описать логической функцией Z=F(A,B)=A & B и таблицей истинности:

| A | B | Z |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Логический вентиль ИЛИ

У логического вентиля ИЛИ, как и у вентиля И, два входа и один выход. Его описывает функция Z=F(A,B)=A v B и таблица истинности:

| A | B | Z |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

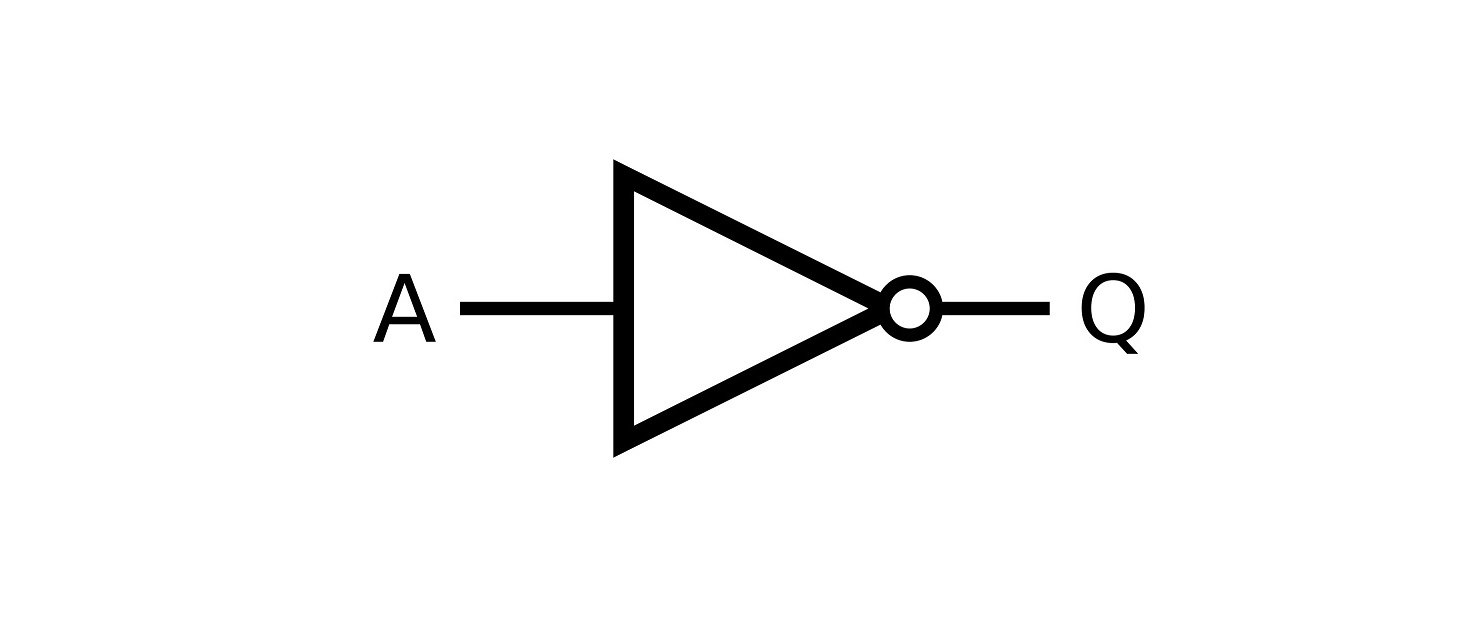

Логический вентиль НЕ

Логический вентиль НЕ имеет только один вход и один выход. На выход поступает инвертированное значение А. Функция вентиля НЕ: Q=F(A)=¬A

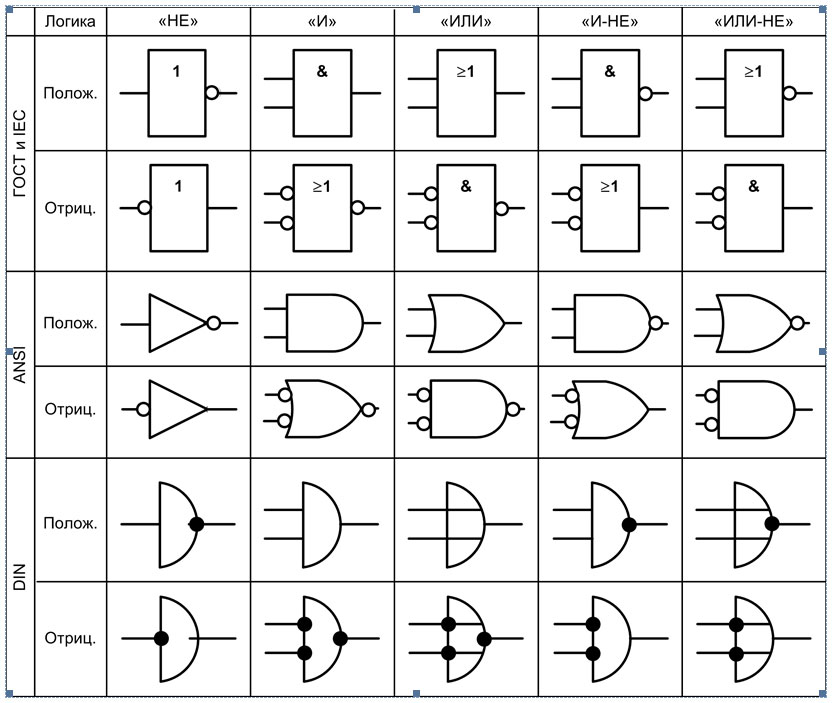

Обозначения по ГОСТ и другим стандартам

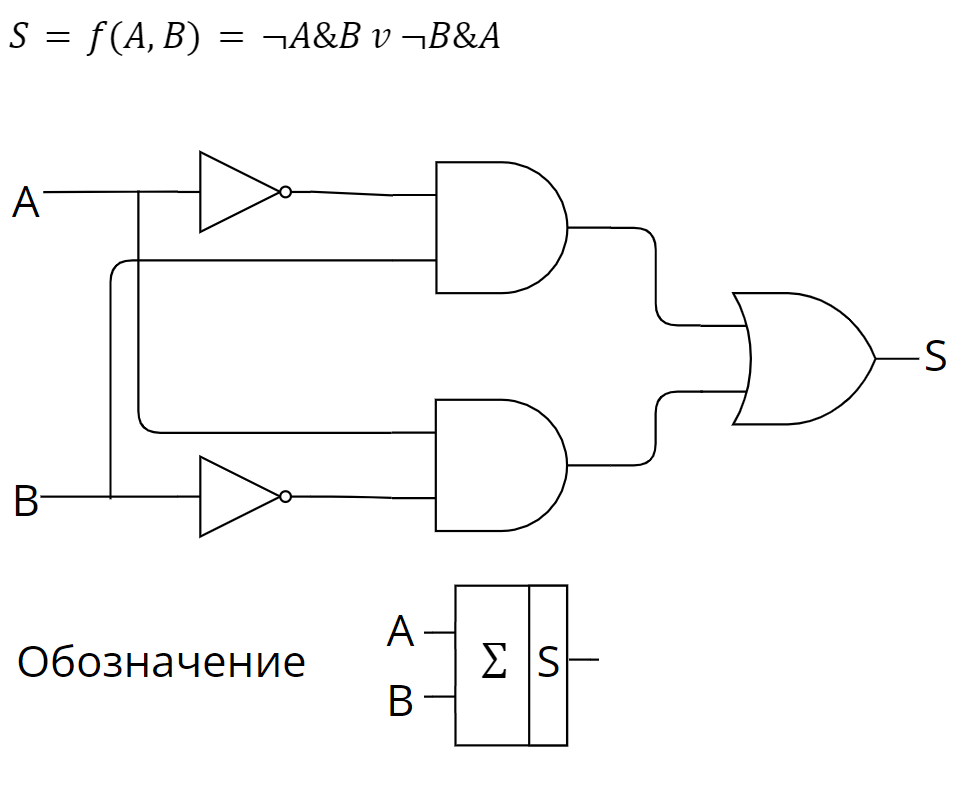

Сумматор

В качестве примера логической схемы, реализующей математическую операцию, рассмотрим многоразрядный двоичный сумматор. Складывать мы будем два двоичных числа. Для построения многоразрядного двоичного сумматора нам понадобится одноразрядный сумматор. Начнем с него.

Разберемся с чем мы будем оперировать: две двоичных цифры. При сложении чисел нам, так или иначе, придется работать с переносом. Например, при сложении двух единиц в двоичной системе счисления мы получим 10:

В случае с одноразрядным сумматором на выход будут поступать две величины: перенос (в данном случае 1) и текущий разряд (0). Пока что мы проигнорируем перенос и составим таблицу истинности для разряда:

| A | B | S |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Имея таблицу истинности, мы можем составить для неё булеву функцию:

Запомним эту функцию.

Добавим в наш сумматор перенос: как с предыдущего разряда (еще один вход), как и для следующего (ещё один выход).

Таблица истинности для сумматора с переносом:

| A | B | P вход | S | P выход |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Теперь необходимо составить две булевы функции: для переноса и новую для разряда.

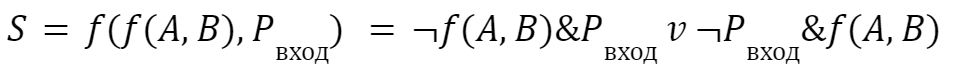

Чисто математически перенос для разряда — это ещё одно слагаемое в сумме. У нас уже есть функция для суммы, воспользуемся ей:

Нам необязательно раскрывать и упрощать эту функцию. Для построения логической схемы такой формы будет достаточно. Определимся с функцией для переноса.

Перенос равен единице в том случае, если из трех входных величин как минимум две равны единицы. Исходя из этого, можно составить вот такую функцию:

На основе двух имеющихся булевых функций для разряда и переноса мы можем составить логическую схему нашего одноразрядного сумматора. Не будем сразу бросаться в бой и начнем со схем поменьше.

Обозначение будет использовано в следующих схемах. Теперь составим схему для функции переноса:

Имея две логические схемы мы можем составить из них одноразрядный двоичный сумматор:

Если несколько одноразрядных сумматоров соединить последовательно, то получится многоразрядный сумматор:

Логическая функция и элемент И-НЕ

Данная функция производит логическое умножение значений входных сигналов, а затем инвертирует результат этого умножения. В логических схемах этот элемент независимо от того, на какой элементной базе он реализован, обозначается так, как показано на рис. 1.4,а. Таблица истинности приведена на рис. 1.4,б.

Если на вход логического элемента И-НЕ подается хотя бы один логический 0, то на его выходе будет логическая 1.

В логических выражениях применяются обозначения:

Схемы определения совпадения сигналов

На логических элементах И, И-НЕ, ИЛИ, ИЛИ-НЕ очень просто реализовать схемы совпадения входящих сигналов, когда выходной сигнал вырабатывается при совпадении логических уровней входящих сигналов. Ниже показаны схемы совпадения на логических элементах.

Реализация функции совпадения сигналов на логических элементах

Вопрос 6

Двоичный код каждого символа при кодировании текстовой информации (в кодах ASCII) занимает в памяти персонального компьютера:

Какой принцип является основополагающим при создании и развитии автоматизированной информационной системы?

Отчет по лабораторным работам по дисциплине

Выполнил студент группы ИВБО-01-18

- Постановка задачи и персональный вариант………….…………. 3

- Восстановленная таблица истинности ………………………………. 3

- Схемы, реализующие логическую функцию на мультиплексорах требуемыми способами ………………………………………………..4

- Реализация логической функции на мультиплексоре 16-1. …….4

- Реализация логической функции на мультиплексоре 8-1…. …. 5

- Реализация логической функции на мультиплексорах 4-1…………….………………………………………………………. 7

- Реализация логической функции на комбинации мультиплексоров 4-1 и 2-1…………………………………………..

- Выводы…………………………………………………………………..9

- Список информационных источников………………………………. 9

- Постановка задачи и персональный вариант.

- Восстановленная таблица истинности

- Схемы, реализующие логическую функцию на мультиплексорах требуемыми способами

- Реализация логической функции на мультиплексоре 4-16

- Реализация логической функции на мультиплексоре 8-1

- Реализация логической функции на мультиплексорах 4-1

- Реализация логической функции на комбинации мультиплексоров 4-1 и 2-1

- Выводы

–используя один мультиплексор 16-1;

–используя один мультиплексора 8-1;

–используя минимальное количество мультиплексоров 4-1;

–используя минимальную комбинацию мультиплексоров 4-1 и 2-1.

Протестировать работу схем и убедиться в их правильности. Подготовить отчет о проделанной работе и защитить ее.

Преобразуем ее в двоичную запись: – получаем столбец значение логической функции, который необходим для восстановления полной таблицы истинности (см. табл.1)

Таблица 1

| a | b | c | d | F |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Для реализации заданной функции на мультиплексоре 16-1 выполним следующее.

Разместим мультиплексор на рабочей области лабораторного комплекса и сделаем ему следующие настройки:

–свойство «выбирающие биты» сделаем равным 4;

–«разрешающий вход» —нет;

–«положение выбирающего входа» —сверху (сделано в данном примере для удобства, можно оставить значение по умолчанию).

Количество информационных входов мультиплексора соответствует количеству значений логической функции. Поэтому просто подадим значения функции на соответствующие входы. Для этого удобно воспользоваться логическими константами из раздела «Провода» библиотеки элементов Logisim.

На адресные (выбирающие) входы мультиплексора подадим при помощи шины значения логических переменных. Несмотря на использование шины, следует помнить, что младшая переменная подается на младший адресный вход, а старшая –на старший.

Собранная и протестированная схема показана на рис. 1. Тестирование подтвердило правильность работы схемы.

Рис. 1 Тестирование схемы, реализующей логическую функцию на мультиплексоре 16-1

Тестирование показало, что схема работает правильно.

Выполним реализацию заданной логической функции при помощи мультиплексора 8-1.

Мультиплексор 8-1 имеет 3 адресных входа, что не позволяет подать на эти входы все 4 логические переменные, как это было сделано в предыдущем случае.

Однако мы можем в качестве адресных переменных выбрать любые три из имеющихся, а оставшуюся четвертую рассматривать наравне с логическими константами как элемент исходных данных для информационных входов.

Удобнее всего в качестве адресных переменных взять три старшие переменные нашей функции, т.е. a, b, c. Тогда пары наборов, на которых эти переменные будут иметь одинаковое значение, будут располагаться в соседних строчках таблицы истинности и поэтому можно будет легко увидеть, как значение логической функции для каждой пары наборов соотносится со значением переменной d(рис. 2).

Например, из рис. видно, что для первой строчки . Всего же для

разных пар наборов же может быть четыре случая: , , , .

Таким образом, мы, по сути, «сжали» функцию от четырех переменных до функции от трех переменных, которая уже имеет необходимые нам реализации для 8 значений. Таблица 2 отображает «сжатую» таблицу истинности.

| a | b | c | d | F |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Рис. 2 Взаимосвязь значений функции и значений переменной «d»

Теперь, рассматривая переменную d наравне с константами 0 и 1 в качестве сигналов для информационных входов мультиплексора 8-1, можно по аналогии с предыдущим случаем выполнить реализацию требуемой функции.

Разместим на рабочей области новый мультиплексор, установим ему количество выбирающих (адресных) входов равным трем, и выполним необходимые соединения (рис. 3)

Рассмотрим реализацию заданной функции на минимальном количестве мультиплексоров 4-1.

Мультиплексор 4-1 имеет 2 адресных входа и 4 информационных. Это означает, что мы должны разбить исходную таблицу истинности на 4 фрагмента, за реализацию каждого из которых в принципе должен отвечать отдельный мультиплексор (назовем его операционным). Однако, необходимо учесть требования минимальности по отношению к количеству используемых мультиплексоров и ставить их только там, где без них нельзя обойтись. Также нам нельзя в рамках данной работы использовать другие логические схемы, за исключением отрицания.

По аналогии с реализацией на дешифраторах 2-4 (см. предыдущую работу), нам обязательно потребуется управляющий мультиплексор, который будет выбирать один из вариантов, предлагаемых операционными мультиплексорами (либо один из очевидных вариантов, если без операционных мультиплексоров можно обойтись).

Разобьем исходную таблицу истинности на зоны ответственности между операционными мультиплексорами, а заодно посмотрим, нельзя ли в некоторых случаях обойтись вообще без операционного мультиплексора (рис. 4).

Первый операционный мультиплексор работает, когда “ ab” равны 00

Второй, когда “ab” равны 01

Третий, когда “ab” равны 10

Четвертый, когда “ab” равны 11

Без первого можно обойтись , поскольку на данном фрагменте F=d

Второй операционный мультиплексор нужен

Третий операционный мультиплексор нужен

Четвертый операционный мультиплексор нужен

| a | b | c | d | F |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

Рис. 4 Разбиение исходной таблицы истинности на зоны ответственности для потенциальных операционных мультиплексоров

Как видно из рис. 3, в одном случае из четырех без операционного мультиплексора можно вполне обойтись. С учетом только что сказанного, схема логической функции на минимальном количестве мультиплексоров 4-1 будет такой, как показано на рис. 5

Реализуем логическую функцию, используя минимальную комбинацию мультиплексоров 4-1 и 2-1. В качестве отправной точки рассмотрим результаты, полученные в предыдущей реализации. Управляющий мультиплексор нельзя заменить на мультиплексор 2-1, поскольку у него на входах уникальные сигналы, а вот операционный заменить можно, поскольку он имеет дело с константами. Из рис. 4 выпишем отдельно фрагменты таблицы истинности, за который данные мультиплексоры отвечают (табл. 3,4,5).

Таблица 3

| c | d | F |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Таблица 4

| c | d | F |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Таблица 5

| c | d | F |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Из таблицы 3 видно, что когда «с» равно 0, то функция равна 1, а когда «с» равно 1, то функция равна не «d». Значит, переменную «с» можно

рассматривать как адресную для мультиплексора 2-1, а не «d» и 1 будут поданы на его информационные входы.

Из таблицы 4 видно, что когда «с» равно 0, то функция равна «d» , а когда «с» равно 1, то функция равна не «d». Значит, переменную «с» можно

рассматривать как адресную для мультиплексора 2-1, а не «d» и «d» будут поданы на его информационные входы.

Из таблицы 5 видно, что когда «с» равно 0, то функция равна не «d» , а когда «с» равно 1, то функция равна 1. Значит, переменную «с» можно

рассматривать как адресную для мультиплексора 2-1, а не «d» и 1 будут поданы на его информационные входы

В результате получим схему, изображенную на рис.6.

В ходе лабораторной работы, я, Косенков Владислав Эдуардович, студент группы ИВБО-01-18 выполнил следующие задачи: восстановил таблицу истинности. По таблице истинности реализовал в лабораторном комплексе логическую функцию на мультиплексорах четырьмя способами: