Основные характеристики пзу компьютера

Основная память — это устройство для хранения информации. Она состоит из оперативного запоминающего устройства (ОЗУ) и постоянного запоминающего устройства (ПЗУ).

Оперативное запоминающее устройство (ОЗУ)

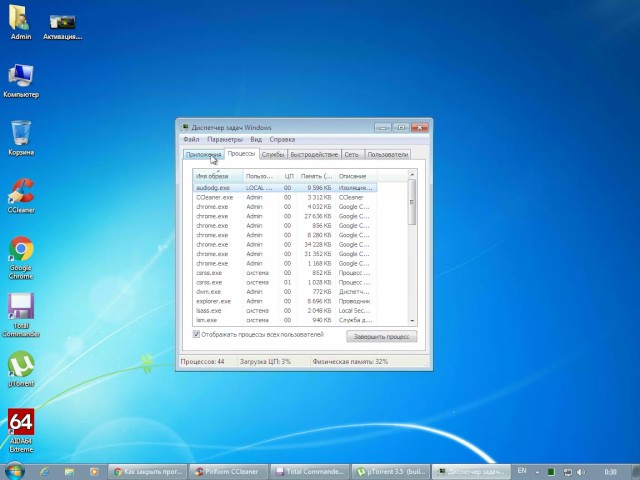

ОЗУ-быстрая, полупроводниковая, энергозависимая память. В ОЗУ хранятся исполняемая в данный момент программа и данные, с которыми она непосредственно работает. Это значит, что когда вы запускаете какую-либо компьютерную программу, находящуюся на диске, она копируется в оперативную память, после чего процессор начинает выполнять команды, изложенные в этой программе. Часть ОЗУ, называемая «видеопамять», содержит данные, соответствующие текущему изображению на экране. При отключении питания содержимое ОЗУ стирается.

Быстродействие (скорость работы) компьютера напрямую зависит от величины его ОЗУ, которое в современных компьютерах может доходить до 128 Мбайт. В первых моделях компьютеров оперативная память составляла не более 1 Мбайт. Современные прикладные программы часто требуют для своего выполнения не менее 4 Мбайт ОЗУ; в противном случае они просто не запускаются.

ОЗУ — это память, используемая как для чтения, так и для записи информации. При отключении электропитания информация в ОЗУ исчезает (энергозависимость).

Постоянное запоминающее устройство (ПЗУ)

ПЗУ — быстрая, энергонезависимая память. ПЗУ — это память, предназначенная только для чтения. Информация заносится в нее один раз (обычно в заводских условиях) и сохраняется постоянно (при включенном и выключенном компьютере). В ПЗУ хранится информация, присутствие которой постоянно необходимо в компьютере.

- тестовые программы, проверяющие при каждом включении компьютера правильность работы его блоков;

- программы для управления основными периферийными устройствами -дисководом, монитором, клавиатурой;

- информация о том, где на диске расположена операционная система.

Основная память состоит из регистров. Регистр — это устройство для временного запоминания информации в оцифрованной (двоичной) форме. Запоминающим элементом в регистре является триггер — устройство, которое может находиться в одном из двух состояний, одно из которых соответствует запоминанию двоичного нуля, другое — запоминанию двоичной единицы. Триггер представляет собой крошечный конденсатор-батарейку, которую можно заряжать множество раз. Если такой конденсатор заряжен — он как бы запомнил значение «1», если заряд отсутствует — значение «0». Регистр содержит несколько связанных друг с другом триггеров. Число триггеров в регистре называется разрядностью компьютера. Производительность компьютера напрямую связана с разрядностью, которая бывает равной 8, 16, 32, 64, 128.

Процессор и основная память находятся на большой плате, которая называется материнской. Для подключения к ней различных дополнительных устройств (дисководов, манипуляторов типа мыши, принтеров и т. д.) служат специальные платы — контроллеры. Они вставляются в разъемы (слоты) на материнской плате, а к их концу (порту), выходящему наружу компьютера, подключается дополнительное устройство.

Запоминающие устройства компьютера — ОЗУ и ПЗУ

На материнской плате компьютера есть оперативное запоминающее устройство (ОЗУ) емкостью несколько мегабайт с малым временем доступа. Эта память используется для временного хранения данных, обрабатываемых центральным процессором. Однако в ОЗУ хранятся не только данные, туда перед запуском должна быть записана программа.

Кроме ОЗУ на материнской плате есть микросхема постоянного запоминающегося устройства (ROM и ПЗУ). Данные

записываются в ПЗУ один раз при изготовлении микросхемы на заводе и обычно не могут быть изменены впоследствии.

В ПЗУ хранятся программы, которые компьютер запускает автоматически при включении питания. Эти программы предназначены для проверки исправности и обслуживания аппаратуры самого компьютера. Они также выполняют первоначальную загрузку главной обслуживающей программы компьютера — так называемой системы

Память на магнитных дисках — устройства внешней памяти, накопители на гибких магнитных дисках и накопители на жестких, предназначены для долговременного хранения информации

ЦИФРОВАЯ СИСТЕМА УПРАВЛЕНИЯ I2C

Цифровая система (шина) управления I2C разработана фирмой Philips для применения в бытовой радиоаппаратуре и, в частности, в телевизорах[12]. Она обеспечивает пересылку цифровой информации (данных) и управление микросхемами, имеющими интерфейсы I2C. Включение последних в состав МС существенно уменьшает число их управляющих выводов и упрощает трассировку печатной платы.

Помимо I2C, существуют и другие разновидности систем (шин) управление аппаратурой, например, S-шина, разработанная фирмой SGS-Thomson, или IM-шина, предложенная фирмой ITT. Однако, система I2C пока наиболее распространена. Ее название происходит от английской аббревиатуры IIC — inter integrated circuit, обозначающей связь между интегральными МС.

I2C представляет собой последовательную двухпроводную магистраль, позволяющую передавать поток цифровой информации в обоих направлениях со скоростью до 100 кбит/с. К магистрали I2C подключают одновременно несколько интегральных МС, причем каждая имеет свой индивидуальный адрес. Ограничением при этом служит суммарная емкость, которая не должна превышать400 пФ. Максимальная длина магистрали — 4 м.

Подключаемые интегральные МС могут быть ведущими, инициирующими обмен информацией (например, микроконтроллеры управления), и ведомыми Причем к магистрали I2C одновременно можно подключить несколько ведущих устройств, так как в ней поддерживается процедура арбитража (состязания). Шина I2C образована двумя двунапрвленными последовательными линиями: данных – SDA и тактовой частоты (синхронизации) – SLC. Каждая линия должна быть подключена к плюсовому проводнику источника питания через резистор R.Схема их пдоключения изображена на рисунке 2.3.1 Выходные каскады МС, подключаемых к шине, имеют открытый сток или открытый коллектор. Резистор R обеспечивает уровень 1 при закрывании всех транзисторов.

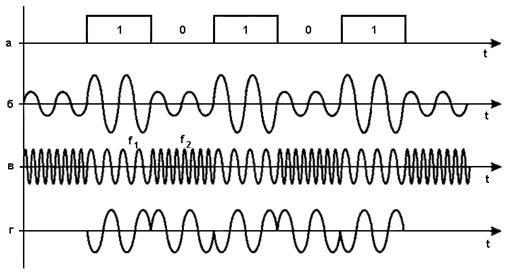

Передача информации по шине I2C обеспечивается по битно. Каждому передаваемому биту по линии SDA соотвеотствует генерируемый тактовый импульс на линии SLC. Передаваемая информация в виде постоянного уровня 1ил 0 на линии SDA в течении тактового импульса на линии SLC (уровень 1) должна быть неизменной. Смена информации происходит только в состоянии 0 линии SLC. Эта ситуация показана на рисунке.

В магистрали I2C передача информации начинается с режима «Старт», а заканчивается режимам «Стоп». Эти условия формируется ведущим устройством и их вид представлен диаграммой на рисунке 2.3.3. Режим «Старт» возникает при переходе уровня на линии SDA из состояния 1 в 0 при уровне 1 на линии SLC. Притом же уровне 1 на линии SLC во время перехода на линии SDA уровня из состояния 0 в1 формируется режим «Стоп».После режима «Старт» магистраль считается занятой и освобождается только после режима «Стоп».

Информация передается по шине I2C в виде последовательных байтов, состоящих из восьми битов, при этом первый передается старший бит. На рисунке 2.3.3 видно, что каждому тактовому импульсу из1-8 на линии SLC соответствует передаваемый бит (1 или 0) на линии SDA. В конце каждого байта информации следует сигнал подтверждения, формируемый на линии SLC приемником. Тактовый импульс подтверждения приема генерируется ведущим устройством (импульс 9 на рисунке 2.3.3). Кроме того, она переводит линию SDA в состояние 1 («отпускает»). При приеме байта информации приемник во время прохождения тактового импульса подтверждения приема должен перевести линию SDA в состояние 0, причем оно действует в течении всего тактового импульса подтверждения. Если приемник, к которому происходит обращение не может принять информацию, линия SDA в момент тактового импульса подтверждения остается в состоянии 1. В этом случае ведущее устройство переходит в режим «Стоп» и прекращает передачу информации. Следовательно, приемник может прервать передачу после любого переданного байта. Кроме того, если приемник не может принять очередной байт, он на некоторое время задерживает передачу информации, переводя линию SCL на уровень 0. Это же происходит и в случае приема каждого бита.

Формат передачи информации по шине показан на рисунке 2.3.4. После формирования режима «Старт» ведущее устройство передает восьмибитную последовательность, состоящую из семибитного адреса приемника, к которому идет обращение, и восьмого бита, определяющего направление передачи информации. После того, как последовательно на шину I2C ведущее устройство подаст сигналы адреса приемника, МС сравнивают семь бит адреса. Если они совпадают для какой-нибудь микросхемы, то она анализирует восьмой бит, чтобы определить направление передачи. Когда этот бит имеет значение 0, ведущее устройство будет передавать информацию приемнику. В случае если бит имеет значение 1, ведущее устройство запросит информацию от приемника.

После того как приемник сформирует сигнал подтверждения адреса (девятый бит), ведущее устройство начинает передавать восьмибитные последовательности информации. Прием каждой последовательности также подтверждается приемником. Передача информации заканчивается формированием режима «Стоп».

Шина I2C позволяет подключать МС, изготовленные по разным технологиям. При работе с напряжениям питания 5 В уровень 0 должен быть не более 1,5 В, уровень 1 — не менее 3 В. Минимальная длительность уровня 0 тактового импульса равна 4,7 мкс, а минимальная длительность уровня 1 тактового импульса равна 4 мкс. Пример использования шины I2C в условном телевизоре цветного изображения показан на рисунке 2.3.5.

Основные структуры запоминающих устройств

Адресные ЗУ представлены в классификации статическими и динамическими оперативными устройствами и памятью типа ROM . Многочисленные варианты этих ЗУ имеют много общего с точки зрения структурных схем, что делает более рациональным не конкретное рассмотрение каждого ЗУ в полном объеме, а изучение некоторых обобщенных структур с последующим описанием запоминающих элементов для различных ЗУ.

Общность структур особенно проявляется для статических ОЗУ и памяти типа ROM . Структуры динамических ОЗУ имеют свою специфику. Для статических ОЗУ и памяти типа ROM наиболее характерны структуры 2 D , 3D и 2 DM .

Структура 2 D

В структуре 2 D , запоминающие элементы ЗЭ организованы в прямоугольную матрицу размерностью

где М — информационная емкость памяти в битах;

k — число хранимых слов;

m — их разрядность.

Структура типа 2 D применяется лишь в ЗУ малой информационной емкости, т. к. при росте емкости проявляется несколько ее недостатков, наиболее очевидным из которых является чрезмерное усложнение дешифратора адреса (число выходов дешифратора равно числу хранимых слов).

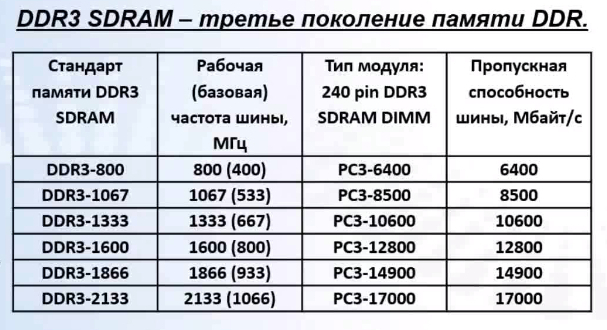

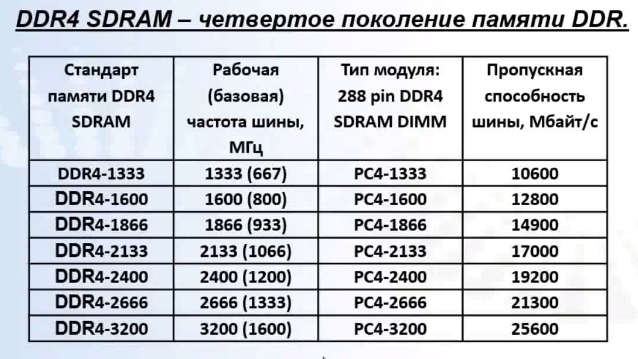

Чем отличаются DDR от DDR2, DDR3 и DDR4

Количеством связывающих ядро с выходным буфером каналов, эффективной частотой, а значит и пропускной способностью памяти. Что касается ширины шины данных (разрядности), то в большинстве современных модулей памяти она составляет 8 байт (64 бит). Допустим, что у нас есть модуль памяти стандарта DDR2-800. Как рассчитать его пропускную способность? Очень просто. Что такое 800? Это эффективная частота памяти в мегагерцах. Умножаем её на 8 байт и получаем 6400 Мб/с.

И последнее. Что такое пропускная способность мы уже знаем, а что такое объём оперативной памяти и зависит ли он от её пропускной способности? Прямой взаимосвязи между этим двумя характеристиками нет. Объём ОЗУ зависит от количества запоминающих элементов. И чем больше таких ячеек, тем больше данных может хранить память без их перезаписи и использования файла подкачки.