Конвейерная архитектура

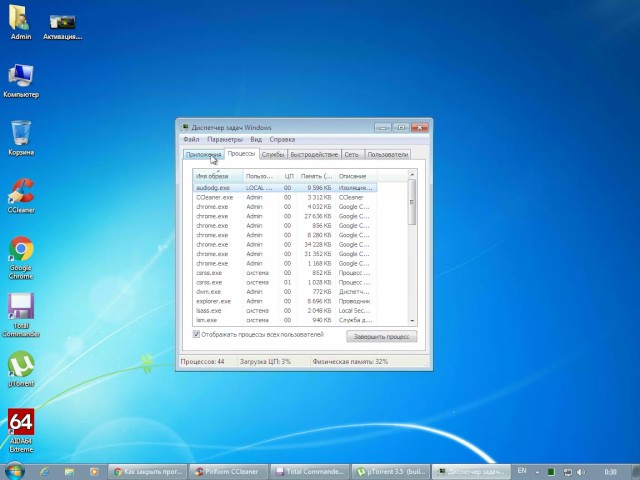

«Схема для компьютера» — Клавиатура Сканер Микрофон Цифровые камеры Цифровые фотоаппараты. Устройства вывода. Схема компьютера. Память. Устройства ввода. Мониторы Принтеры Наушники, колонки Плоттеры (графопостроители). Внутренняя (оперативная) Внешняя. Как же происходит движение информации в ходе работы компьютера? Процессоры.

«Архитектура персонального компьютера» — Принцип общего устройства. Процессор. Видеопамять. Тактовая частота. Устройства памяти. Принцип произвольного доступа. Описание устройств. Модули памяти. Постоянная память. Функциональная схема ПК. Внутренняя память. Машина. Энергонезависимая память. Принцип хранимой программы. Память с невысоким быстродействием.

«Архитектура и устройство компьютера» — Интерфейс. Жесткий диск. Критерии при выборе процессора. Центральное обрабатывающее устройство. Диск. Поддержка оперативной памяти. Системная шина. Принцип построения компьютера. Магистраль. Материнская плата. Параметр. Внимание. Архитектура компьютера. Модульность. Процессор. Размер материнкой платы.

«Архитектура компьютера» — Модемы бывают внутренними. Матричный принтер. Стример. Графический акселератор. Модем. Графический планшет. Графопостроитель. Звуковая карта. Системный блок может быть выполнен по- разному. На дискетах 5.25 дюймов имеется прорезь для защиты от записи. Логическая схема системной платы. Гибкие диски. Оперативная память, предназначенная для хранения информации.

«Архитектура современного компьютера» — Количество битов. Процессор. Архитектура компьютера. Магистрально-модульный принцип. Оперативная память. Компьютер. Пересылка данных. Описание устройства. Последовательность команд. Постоянная память. Данные и программы. Устройства ввода и вывода информации. Структурная схема компьютера.

«Машина ЭВМ» — История развития вычислительной техники. Коэффициент усиления по мощности: Логический элемент И-НЕ серии ТТЛ. Механические вычислительные устройства. Архитектура ЭВМ. Динамические параметры цифровых интегральных схем. Варианты подключения нагрузки к транзисторному ключу. Классификация ЭВМ. Статические характеристики цифровых интегральных схем.

Системы классификации архитектур компьютеров

В 1966 г. М.Флинном (Flynn) был предложен чрезвычайно удобный подход к классификации архитектур вычислительных систем. В его основу было положено понятие потока, под которым понимается последовательность элементов, команд или данных, обрабатываемая процессором. Соответствующая система классификации основана на рассмотрении числа потоков инструкций и потоков данных и описывает четыре архитектурных класса:

SISD (single instruction stream / single data stream) – одиночный поток команд и одиночный поток данных. К классу SISD относятся последовательные компьютерные системы, которые имеют один центральный процессор, способный обрабатывать только один поток последовательно исполняемых инструкций. В настоящее время практически все высокопроизводительные системы имеют более одного центрального процессора, однако каждый из них выполняет несвязанные потоки инструкций, что делает такие системы комплексами SISD-систем, действующих на разных пространствах данных. Для увеличения скорости обработки команд и скорости выполнения арифметических операций может применяться конвейерная обработка. В случае векторных систем векторный поток данных следует рассматривать как поток из одиночных неделимых векторов. Примерами компьютеров с архитектурой SISD могут служить большинство рабочих станций Compaq, Hewlett-Packard и Sun Microsystems;

MISD (multiple instruction stream / single data stream) – множественный поток команд и одиночный поток данных. Теоретически в этом типе машин множество инструкций должно выполняться над единственным потоком данных. До сих пор ни одной реальной машины, попадающей в данный класс, создано не было;

SIMD (single instruction stream / multiple data stream) – одиночный поток команд и множественный поток данных. Эти системы обычно имеют большое количество процессоров, от 1024 до 16384, которые могут выполнять одну и ту же инструкцию относительно разных данных в жесткой конфигурации. Единственная инструкция параллельно выполняется над многими элементами данных. Примерами SIMD-машин являются системы CPP DAP, Gamma II и Quadrics Apemille. Другим подклассом SIMD-систем являются векторные компьютеры. Векторные компьютеры манипулируют массивами сходных данных подобно тому, как скалярные машины обрабатывают отдельные элементы таких массивов. Это делается за счет использования специально сконструированных векторных центральных процессоров. Когда данные обрабатываются посредством векторных модулей, результаты могут быть выданы на один, два или три такта частотогенератора (такт частотогенератора является основным временным параметром системы). При работе в векторном режиме векторные процессоры обрабатывают данные практически параллельно, что делает их в несколько раз более быстрыми, чем при работе в скалярном режиме. Примерами систем подобного типа являются, например, компьютеры Hitachi S3600;

MIMD (multiple instruction stream / multiple data stream) – множественный поток команд и множественный поток данных. Эти машины параллельно выполняют несколько потоков инструкций над различными потоками данных. В отличие от многопроцессорных SISD-машин, команды и данные связаны, потому что они представляют различные части одной и той же задачи. Например, MIMD-системы могут параллельно выполнять множество подзадач с целью сокращения времени выполнения основной задачи. Большое разнообразие попадающих в данный класс систем делает классификацию Флинна не полностью адекватной. Действительно, и четырехпроцессорный SX-5 компании NEC, и тысячепроцессорный Cray T3E попадают в этот класс. Это заставляет использовать другой подход к классификации, иначе описывающий классы компьютерных систем. Основная идея такого подхода может состоять, например, в следующем. Будем считать, что множественный поток команд может быть обработан двумя способами: либо одним конвейерным устройством обработки, работающем в режиме разделения времени для отдельных потоков, либо каждый поток обрабатывается своим собственным устройством. Первая возможность используется в MIMD-компьютерах. Их обычно называют конвейерными или векторными, вторая – в параллельных компьютерах. В основе векторных компьютеров лежит концепция конвейеризации, т.е. явного сегментирования арифметического устройства на отдельные части, каждая из которых выполняет свою подзадачу для пары операндов. В основе параллельного компьютера лежит идея использования для решения одной задачи нескольких процессоров, работающих сообща, причем процессоры могут быть как скалярными, так и векторными.

Для параллельных компьютерных систем существует своя классификация.

I. Векторно-конвейерные компьютеры (PVP).

Имеют MIMD-архитектуру. Основные особенности:

· конвейерные функциональные устройства;

· набор векторных инструкций в системе команд;

· зацепление команд (используется как средство ускорения вычислений).

II. Массивно-параллельные компьютеры с распределенной памятью.

Объединяется несколько серийных микропроцессоров, каждый со своей локальной памятью, посредством некоторой коммуникационной среды.

Достоинств у такой архитектуры много: если нужна высокая производительность, то можно добавить еще процессоров; если ограничены финансы или заранее известна требуемая вычислительная мощность, то легко подобрать оптимальную конфигурацию и т.д.

Каждый процессор имеет доступ лишь к своей локальной памяти, а если программе нужно узнать значение переменной, расположенной в памяти другого процессора, то задействуется механизм передачи сообщений. Этот подход позволяет создавать компьютеры, включающие в себя тысячи процессоров.

Но эта архитектура имеет два существенных недостатка:

· требуется быстродействующее коммуникационное оборудование, обеспечивающее среду передачи сообщений;

· при создании программ необходимо учитывать топологию системы и специальным образом распределять данные между процессорами, чтобы минимизировать число пересылок и объем пересылаемых данных.

Последнее обстоятельство и мешает широкому внедрению подобных архитектур.

III. Параллельные компьютеры с общей памятью (SMP).

Вся оперативная память разделяется между несколькими одинаковыми процессорами. Это снимает проблемы предыдущего класса, но добавляет новые — число процессоров, имеющих доступ к общей памяти, нельзя сделать большим.

Основное преимущество таких компьютеров — относительная простота программирования. В ситуации, когда все процессоры имеют одинаково быстрый доступ к общей памяти, вопрос о том, какой процессор какие вычисления будет выполнять, не столь принципиален, и значительная часть вычислительных алгоритмов, разработанных для последовательных компьютеров, может быть ускорена с помощью распараллеливающих и векторизирующих трансляторов. SMP-компьютеры — это наиболее распространенные сейчас параллельные вычислители. Однако общее число процессоров в SMP-системах, как правило, не превышает 16, а их дальнейшее увеличение не дает выигрыша из-за конфликтов при обращении к памяти.

IV. Кластерная архитектура.

Кластерная архитектура представляет собой комбинации предыдущих трех. Из нескольких процессоров (традиционных или векторно-конвейерных) и общей для них памяти формируется вычислительный узел. Если полученной вычислительной мощности не достаточно, то объединяется несколько узлов высокоскоростными каналами.

Другие распространенные критерии классификации компьютеров.

Классификация по назначению:

· большие электронно-вычислительные машины (ЭВМ) или Main Frame;

Классификация по уровню специализации [2, 5, 6, 8, 13, 15, 18]:

Классификация по раз меру:

Классификация по совместимости:

· аппаратная совместимость (платформа IBM PC и Apple Macintosh);

· совместимость на уровне операционной системы;

· совместимость на уровне данных.

Таким образом, выбрав в качестве критериев классификации выше перечисленные признаки, в первую очередь, вычислительную мощность и габариты, получем слудующую схему:

Следует заметить, что любая классификация является в некоторой мере условной, поскольку развитие компьютерной науки и техники настолько бурное, что, например, сегодняшняя микро ЭВМ не уступает по мощности мини ЭВМ суперкомпьютерам недавнего прошлого. Кроме того, зачисление компьютеров к определенному классу довольно условно через нечеткость разделения групп, так и вследствии внедрения в практику заказной сборки компьютеров, где номенклатуру узлов и конкретные модели адаптируют к требованиям заказчика.

В организации цифровой вычислительной системы можно выделить девять уровней иерархии:

Первый уровень, физический, объединяет в себе физические законы, явления и эффекты, лежащие в основе создания и функционирования аппаратной составляющей вычислительной системы. Это уровень интегральной и функциональной микроэлектроники, обеспечивающей элементную базу вычислительной аппаратуры.

Второй уровень, уровень аналоговой схемотехники, связан с построением базовых логических элементов (вентилей) из аналоговых компонентов (диодов, транзисторов, емкостей и т.д.).

Третий уровень, уровень цифровой схемотехники, определяет принципы, модели и методы построения функциональных узлов и устройств аппаратуры в заданном логическом базисе. Этот уровень имеет свою внутреннюю иерархию, которая детально представлена в разделе главы.

Четвертый уровень, уровень системотехники, определяет общую структуру вычислительной системы, организацию взаимосвязей ее подсистем и модулей между собой, выбор оптимальных режимов функционирования и т.д. Это уровень, отражающий принципы построения и закономерности функционирования системы в целом с учетом влияния внешних факторов, технико-экономических и других показателей. На этом уровне в первом приближении распределяются функции между аппаратной и программной составляющими архитектуры вычислительной системы.

Пятый уровень, микроархитектурный, связан с организацией управления аппаратными средствами компьютера на языке микрокоманд. Это уровень интерпретации машинных команд, на котором реализуются (аппаратно или микропрограммно) эффективные технологии исполнения инструкций с применением упреждающей выборки команд, конвейеризации, распараллеливания, кэширования, динамического предсказания ветвлений, переименования регистров и других приемов, способствующих повышению эффективности вычислительного процесса.

Шестой уровень, уровень машинных команд, представляет набор команд (инструкций), выполняемых аппаратными средствами или микропрограммой-интерпретатором. Это связующее звено между аппаратным и программным обеспечением, поэтому организация его должна быть рациональной как с точки зрения разработчиков аппаратного обеспечения, так и с точки зрения создателей программ-трансляторов с языков высокого уровня.

Седьмой уровень, уровень операционной системы, отличается от предыдущего наличием дополнительных команд, своей организации памяти, мультипрограммного режима и других расширений, реализуемых специальным интерпретатором, построенным на базе шестого и возможно пятого уровней и называемым операционной системой.

Последние три из рассмотренных уровней изначально планируются как инструментальная среда для создания системного программного обеспечения (трансляторов, оболочек операционных систем и других расширений, поддерживающих языки более высоких уровней). В отличие от них, средства восьмого и девятого уровней ориентируются на прикладных программистов.

Пример 1 — понятие и виды. Классификация и особенности категории «Пример 1» 2017, 2018.

По дороге движутся два грузовых автомобиля, один порожний, другой с грузом на платформе. Требуется определить, какие максимальные скорости движения на поворотах с радиусом R= 50 м могут быть допущены для обоих автомобилей, не вызывая их бокового опрокидывания. Исходные. [читать подробнее].

Двигатели последовательного возбуждения являются саморегулирующимися, так как при увеличении нагрузки уменьшаются обороты и увеличивается момент и наоборот. Эти двигатели наиболее подходят к условиям тяги поездов и поэтому получили широкое. [читать подробнее].

Нисходящее и восходящее проектирование. Если решение задач высоких иерархических уровней предшествует решению задач более низких иерархических уровней, то проектирование называют нисходящим. Если раньше выполняются этапы, связанные с низшими иерархическими уровнями. [читать подробнее].

Наиболее простыми и широко используемыми контактными устройствами центральной части, предназначенными для логической обработки информации, являются электромагнитные реле.Подробная классификация, принципы действия, конструкции, основные характеристики и параметры. [читать подробнее].

В машиностроении базовые элементы представлены деталями. Примерами деталей являются винт, шпонка, маслоотражатель, вал, зубчатое колесо. Детали рассматриваются как элементы, фигурирующие в описаниях низшего иерархического уровня, на котором системами являются. [читать подробнее].

В качестве датчика управляемой величины используется поплавок 1; в качестве задающего устройства – фиксатор поплавка 2. Поплавок с помощью рычага 3 перемещает контактный ползунок потенциометрического датчика 4. Датчик управляет исполнительным устройством – реверсивным. [читать подробнее].

Рис 1.1. Объект управления Заданный алгоритм обычно предусматривает поддержание рабочего параметра постоянным во времени или же изменение во времени по известному или неизвестному закону. Задача управления, по существу, заключается в формировании такого закона. [читать подробнее].

Примеры трансформационных упражнений Примеры подстановочных упражнений 1. Составьте предложения из заданных слов. 2. Составьте предложения по образцу. 3. Прослушайте диалог, воспроизведите его и составьте диалог по аналогии. 4. Расскажите о себе или друге. [читать подробнее].

Тренировка грамматического материала Примеры упражнений на первичное закрепление материала. 1. Сравните употребление . в следующих ситуациях и скажите, по какому признаку они противопоставлены. 2. Сравните ситуации, найдите общее и отличительное в. [читать подробнее].

Пример 8. Свободно опертая по контуру плита перекрытия крупнопанельного здания (рис. 53). Исходные данные. Размеры плиты в плане — 3580 ´ 6580 мм. Толщина 120 мм. Размеры опорных площадок: вдоль короткого пролета — 50мм; вдоль длинного пролета — 70 мм. Расчетные пролеты плиты: l1 =. [читать подробнее].

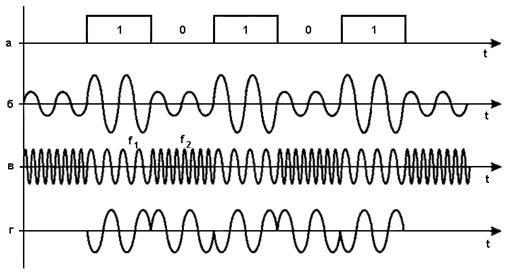

Конвейерные процессоры

Процессоры современных компьютеров используют особенную технологию — конвейеры, которые позволяют обрабатывать более одной команды одновременно.

Обработка команды может быть разделена на несколько основных этапов, назовем их микрокомандами . Выделим основные пять микрокоманд:

- • выборка команды;

- • расшифровка команды;

- • выборка необходимых операндов;

- • выполнение команды;

- • сохранение результатов.

Все этапы команды задействуются только один раз и всегда в одном и том же порядке: одна за другой. Это, в частности, означает, что если первая микрокоманда выполнила свою работу и передала результаты второй, то для выполнения текущей команды она больше не понадобится, и, следовательно, может приступить к выполнению следующей команды. Выделим каждую команду в отдельную часть устройства и расположим их в порядке выполнения. В первый момент времени выполняется первая микрокоманда. Она завершает свою работу и начинает выполняться вторая микрокоманда, в то время как первая готова для выполнения следующей инструкции. Первая инструкция может считаться выполненной, когда завершат работу все пять микрокоманд.

Такая технология обработки команд носит название конвейерной обработки. Каждая часть устройства называется ступенью конвейера, а общее число ступеней — длиной конвейера.

Во многих вычислительных системах наряду с конвейером команд используются и конвейеры данных.

Сочетание этих двух конвейеров позволяет достичь очень высокой производительности на определенных классах задач, особенно если используется несколько различных конвейерных процессоров, способных работать одновременно и независимо друг от друга.

Одной из наиболее высокопроизводительных вычислительных конвейерных систем считается CRAY. В этой системе конвейерный принцип обработки используется в максимальной степени. Имеется и конвейер команд, и конвейер арифметических и логических операций. В системе широко применяется совмещенная обработка информации несколькими устройствами. Максимальная пиковая производительность процессора может составлять 12 GFLOPS.

В настоящее время созданы однокристальные векторно-конвейерные процессоры, основными компонентами которых являются скалярный процессор и 8 идентичных векторных устройств, суммарная производительность которых составляет 64 GFLOPS. На их основе построена система SX-6 компании NEC.

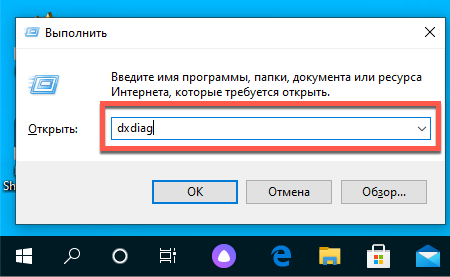

Конвейерная архитектура

Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифровка команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. Например, конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии:

получение и декодирование инструкции,

адресация и выборка операнда из ОЗУ,

выполнение арифметических операций,

сохранение результата операции.

После освобождения k-й ступени конвейера она сразу приступает к работе над следующей командой. Если предположить, что каждая ступень конвейера тратит единицу времени на свою работу, то выполнение команды на конвейере длиной в n ступеней займёт n единиц времени, однако в самом оптимистичном случае результат выполнения каждой следующей команды будет получаться через каждую единицу времени.

Действительно, при отсутствии конвейера выполнение команды займёт n единиц времени (так как для выполнения команды по-прежнему необходимо выполнять выборку, дешифровку и т. д.), и для исполнения m команд понадобится единиц времени; при использовании конвейера (в самом оптимистичном случае) для выполнения m команд понадобится всего лишь n + m единиц времени.

Факторы, снижающие эффективность конвейера:

Простой конвейера, когда некоторые ступени не используются (напр., адресация и выборка операнда из ОЗУ не нужны, если команда работает с регистрами).

Ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой (это преодолевается при использовании внеочередного выполнения команд — out-of-order execution).

Очистка конвейера при попадании в него команды перехода (эту проблему удаётся сгладить, используя предсказание переходов).

Некоторые современные процессоры имеют более 30 ступеней в конвейере, что увеличивает производительность процессора, однако приводит к большому времени простоя (например, в случае ошибки в предсказании условного перехода). Не существует единого мнения по поводу оптимальной длины конвейера: различные программы могут иметь существенно различные требования.

Суперскалярная архитектура

Способность выполнения нескольких машинных инструкций за один такт процессора путем увеличения числа исполнительных устройств. Появление этой технологии привело к существенному увеличению производительности, в то же время существует определенный предел роста числа исполнительных устройств, при превышении которого производительность практически перестает расти, а исполнительные устройства простаивают. Частичным решением этой проблемы являются, например, технология Hyper Threading.

CISC-процессоры

Complex instruction set computer — вычисления со сложным набором команд. Процессорная архитектура, основанная на усложнённом наборе команд. Типичными представителями CISC являются микропроцессоры семейства x86 (хотя уже много лет эти процессоры являются CISC только по внешней системе команд: в начале процесса исполнения сложные команды разбиваются на более простые микрооперации (МОП’ы), исполняемые RISC-ядром).

RISC-процессоры

Reduced instruction set computer — вычисления с упрощённым набором команд (в литературе слово «reduced» нередко ошибочно переводят как «сокращённый»). Архитектура процессоров, построенная на основе упрощённого набора команд, характеризуется наличием команд фиксированной длины, большого количества регистров, операций типа регистр-регистр, а также отсутствием косвенной адресации.

Концепция RISC разработана Джоном Коком (John Cocke) из IBM Research, название придумано Дэвидом Паттерсоном (David Patterson).

Упрощение набора команд призвано сократить конвейер, что позволяет избежать задержек на операциях условных и безусловных переходов. Однородный набор регистров упрощает работу компилятора при оптимизации исполняемого программного кода. Кроме того, RISC-процессоры отличаются меньшим энергопотреблением и тепловыделением.

Среди первых реализаций этой архитектуры были процессоры MIPS, PowerPC, SPARC, Alpha, PA-RISC. В мобильных устройствах широко используются ARM-процессоры.

MISC-процессоры

Minimum instruction set computer — вычисления с минимальным набором команд. Дальнейшее развитие идей команды Чака Мура, который полагает, что принцип простоты, изначальный для RISC-процессоров, слишком быстро отошёл на задний план. В пылу борьбы за максимальное быстродействие, RISC догнал и перегнал многие CISC процессоры по сложности. Архитектура MISC строится на стековой вычислительной модели с ограниченным числом команд (примерно 20-30 команд).

VLIW-процессоры

Very long instruction word — сверхдлинное командное слово. Архитектура процессоров с явно выраженным параллелизмом вычислений, заложенным в систему команд процессора. Являются основой для архитектуры EPIC. Ключевым отличием от суперскалярных CISC-процессоров является то, что для них загрузкой исполнительных устройств занимается часть процессора (планировщик), на что отводится достаточно малое время, в то время как загрузкой вычислительных устройств для VLIW-процессора занимается компилятор, на что отводится существенно больше времени (качество загрузки и, соответственно, производительность теоретически должны быть выше). Примером VLIW-процессора является Intel Itanium.