Программируемые логические контроллеры: принцип работы, виды и применение

В 60 годах 20 века для управления телефонными станциями, промышленным оборудованием использовались сложные схемы с реле. Они не отличались повышенной надежностью или ремонтопригодностью. Инженерам одной из компаний, американской General Motors, была поставлена цель по созданию нового оборудования. Задачи, на которые оно было рассчитано, выглядели так:

- Упрощение отладки, замены.

- Относительная дешевизна.

- Гибкость, удобство модернизации.

- Снижение риска отказов.

Изобретение, создание микросхем и блоков управления на их основе позволило решить заданные вопросы.

Терминология, объясняющая, что такое ПЛК (PLC), внесена в международные и европейские стандарты качества МЭК, EN.

Что такое сетевой контроллер для Windows 7 или любой другой системы и для чего он используется?

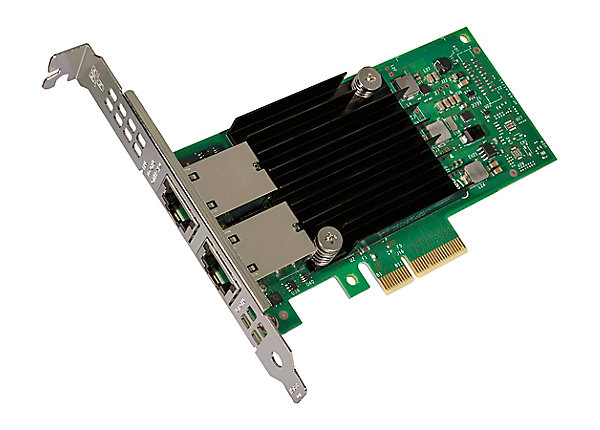

Обычно под сетевым контроллером подразумевают самые обычные сетевые карты, которые вместе с установленными для них драйверами, а иногда и с дополнительным программным обеспечением отвечают за подключение компьютерных систем к локальным и виртуальным сетям, а также обеспечивают выход в интернет. Таким образом, сетевой контроллер для Windows 7 или любой другой ОС (необязательно Windows) может быть представлен в виде двух основных типов

Во-первых, все устройства можно подразделить на два основных типа – железные и виртуальные. Первые, как уже понятно, представляют собой оборудование, устанавливаемое чаще всего непосредственно на материнской плате. Ко второму типу относятся специальные программные компоненты, которые тоже являются своего рода посредниками для доступа к локальным и виртуальным сетям или к интернету, но выполнены исключительно в виде специального программного обеспечения (например, виртуальные туннельные адаптеры). Сетевые платы «железного» типа могут быть проводными и беспроводными.

На проводных имеются специальные гнезда для подключения сетевых кабелей. К беспроводным контроллерам можно отнести всевозможные модули, позволяющие осуществить сетевой доступ с компьютера или к компьютеру без прямого соединения с другими устройствами (например, модули Wi-Fi). И те и другие могут быть как встроенного, так и внешнего типа. Первые, как уже говорилось, устанавливаются прямо на материнской плате, а вторые могут подключаться через дополнительные интерфейсы вроде USB. Иногда можно встретить и девайсы совмещенного типа.

Применение

Микроконтроллер обладает явной простотой: требуется меньше аппаратного обеспечения, с ним легче работать на программном уровне, да и стоимость начинается с копеек. Но эта простота касается и производительности. Как говорилось выше, микроконтроллер не способен обеспечить высокую производительность наравне с микропроцессорами. Микропроцессоры хоть и требуют внешней коммутации «железа» и относительно МК сложны в работе, но они уже спокойно могут применяться в более сложных устройствах.

Однако иногда в сети появляются умельцы, которые впихивают в микроконтроллер ESP32 DOOM и даже эмулятор NES-игр.

Драйвера

Существуют так называемые базовые драйвера, которые можно классифицировать как более или менее универсальные. В сети можно найти множество платных и бесплатных файлов. Нужно помнить о вирусном риске, поэтому не забудьте проверить активность антивируса перед началом загрузки.

Как же выбрать файл, который подойдет именно вашей операционной системе, и не вызовет впоследствии проблем со скоростью и общим качеством работы? Ниже приведены названия файлов и версии операционных систем, которым они подходят:

- exe—Windows x 86 (32 разряда).

- exe—Windows x 64 (64 разряда).

Для того чтобы скачивание и последующая работа с контентом прошла успешно, проверьте безопасность содержимого. После скачивания файла, который предоставляется в виде архива, его необходимо распаковать и запустить. Все заархивированные документы перенесутся во временную директорию, так как обычно они имеют очень большие размеры, что может замедлить работу ПК. После запуска мастера установок, можно удалять все временные документы.

Универсальные драйвера станут спасение для тех, кто, мягко говоря, относит себя к категории «чайников». Они не привередливы в установке, и достаточно легкодоступны для скачивания. Следует помнить о том, что название «Универсальный драйвер» условное, так как невозможно разработать продукт, который сможет удовлетворить потребности как старенького компьютера, занимающего целый стол, так и новомодного ноутбука, который легко можно спутать с напольными весами.

Материалы и цвет

Качественные материалы влияют на удобство использования и долговечность устройства. Качественный пластик позволяет избавиться от люфтов и зазоров. Противоскользящие материалы, примененные в местах хвата (и на стиках), повышают его удобство, особенно когда ладони потеют во время долгих и напряженных игровых сессий. Кроме того, устройство из качественных материалов, гораздо приятнее держать в руках, чем дешевые поделки.

Синхронизация подсистемы памяти

В подсистеме памяти чаще всего различают три частотных домена: системный домен, домен контроллера памяти и домен самой памяти. Пример представлен ниже.

Решение проблемы синхронизации включает в себя следующие вопросы: какие тактовые частоты будут у доменов и каким образом они будут взаимодействовать в совокупности. От этого будет зависеть задержка обращения в память и максимально допустимая частота памяти, ведь частота контроллера памяти может её ограничить. Итак, синхронизация подсистемы памяти влияет на её эффективность.

Для начала рассмотрим проблему метастабильности на примере триггеров. Что такое триггеры? Это защелки, которые синхронизируются на фронте или спаде тактового импульса. Много непонятных слов? О том, как работают защелки знать не обязательно. Достаточно понимать, что защелка может хранить один бит информации. Но синхронная защелка может записать бит информации только тогда, когда на одном из входов защелки есть тактовый импульс. Таким образом, тактовый импульс является своего рода сигналом, что данные с входа данных можно записать. А триггер отличается тем, что ему нужен не весь тактовый импульс, а только его фронт или спад.

В нашем случае триггеры будут синхронизироваться по фронтам, так что далее рассматривать будем только фронт, но помним, что для спада всё то же самое.

Для правильной работы триггера необходимо, чтобы входные данные триггера некоторое время оставались неизменны до фронта импульса. Этот временной интервал называется Time Setup (Ts). Аналогично после фронта импульса данные также некоторое время должны оставаться неизменными, и это временное требование называется Time Hold (Th).

Если требования для входных данных выполняются, то на выходе триггера данные также появляются. А иначе верное выходное значение триггера устанавливается через большее время. Такое состояние называется метастабильностью. В метастабильном состоянии сигнал пребывает в состоянии, которое нельзя назвать ни логическим нулём, ни логической единицей. Дальнейшее распространение метастабильного сигнала может привести к сбою всей системы.

Данная проблема характерна для передачи данных между доменами с разными частотами. Вы узнаете почему позже, а пока просто покажу частоты доменов подсистемы памяти в разных проектах.

Эльбрус-С+:

системный домен с частотой 500 МГц (системная частота);

домен оперативной памяти, частота которого относится к системной как 4/5, 2/3, 3/5 или 1/2;

домен ядра контроллера оперативной памяти, отношение его частоты к частоте памяти равно 1/2.

Один из КП А.С Кожина:

Системный домен (System domain) – 800/1000 МГц

Домен оперативной памяти (DDR domain) – 800, 666, 533, 400 МГц

Домен ядра контроллера (MC domain) – частота в 2 раза ниже частоты памяти

Домен оперативной памяти ровно в два раза меньше эффективной частоты оперативной памяти.

В двух случаях мы наблюдаем подсистему памяти, частотные домены которой имеют разные частоты (логично).

Возвращаемся к проблеме метастабильности. На рисунке (а) мы видим, что фронт CLKB захватывает нестабильный сигнал DA. Временной интервал между фронтами оказался недостаточным. В итоге мы имеем метастабильный сигнал DB.

Одними из решений данной проблемы является добавление ещё одного триггера. Совокупность триггеров на приемной стороне образует синхронизатор (рисунок б). Дополнительный триггер помог избавиться от дальнейшего распространения метастабильности сигналов, ведь DB2 принимает правильное значение. Однако не всегда такой синхронизатор решает проблему метастабильности. Например, здесь.

В первом случае CLKB не успевает захватить сигнал данных DA, а во втором случае CLKB захватывает DA три раза, то есть по сути одиночную посылку воспринимает, как множество посылок. В первом случае наблюдается передача из высокочастного домена в низкочастотный домен, а во втором — из низкочастотного в высокочастотный. Рассмотрим другой метод.

Стандартной, самой распространенной схемой пересинхронизации является асинхронный FIFO-буфер. Асинхронный FIFO-буфер отличается от синхронного тем, что асинхронный работает с двумя тактовыми доменами: wrclk и rdclk. Здесь представлен FIFO-буфер от Altera. Модуль Write Control Logic осуществляет передачу в блок памяти (на рисунке Altera Memory Block), а Read Control Logic обеспечивают прием данных. Write Pointer и Read Pointer содержат указатели на ячейки буфера, задействованные в данный момент времени.

W_ADR соответствует значению Write Pointer, R_ADR соответствует значению Write Read.

Так как буфер асинхронный, то и write control logic, и read control logic функционируют на разных частотных доменах (имеют разные частоты).

Блок Flag Logic служит для формирования информационных сигналов о заполнении. Ниже представлена та же схема на более низком уровне.

Сначала указатель записи формируется в модуле в GRAYCOUNTER в коде Грея. Код Грея характерен тем, что в последовательности предыдущее значение от данного отличается только одним битом.

То есть в двоичной системе счисления будет так:

000

001 (отличается от предыдущего(000) одним битом)

010 (отличается от предыдущего(001) уже двумя битами в двух позициях)

011

100 (а здесь данное слово отличается всеми тремя битами от предыдущего)

101

110

111

Тогда как в коде Грея это будет выглядеть вот так:

000

001

011

010

110

111

101

100

Если мы возьмем любое значение, то опять же увидим, что оно отличается от предыдущего и от следующего только одним битом в какой-либо позиции. А зачем он нужен здесь вы узнаете совсем скоро. Далее из GRAYCOUNTER данные указателя отправляются в приемник через шину wrptr_g, а приемник работает на другой частоте. Здесь под шиной мы понимаем только совокупность проводников, по которым идет по биту информации. Но для исключения метастабильности на этом этапе к каждой линии шины подведен дополнительный триггер на передающей стороне, на рисунке он также изображен, и три триггера на принимающей стороне (на рисунке синхронизатор). Тогда возможно такое (при изменении указателя записи, то есть данных в GRAYCOUNTER), что сигналы на линиях шины будут задержаны относительно друг-друга, а это приведет к тому, что в одних линиях приемник захватит новые значения, а в других — старые. А в коде Грея новое значение отличается всего на один бит. У нас будет всего два варианта: либо старое (пусть будет 011), либо новое значение (пусть будет 010). А это к сбою работы FIFO-буфера не приведет. Далее gray2bin модуль сможет преобразовать код Грея в двоичное число. Также в любом FIFO-буфере с помощью сравнений указателей записи и чтения, узнается пуст ли или полон буфер. Верхняя граница известна, а при равенстве указателей мы понимаем, что буфер пуст. Ведь нельзя считать пустотой буфер или записать данные в переполненный, так что устанавливаются флаги из Flag Logic.

Асинхронные FIFO-буферы используются очень часто из-за того, что они могут передать данные доменов с очень разным соотношением частот. Да и вообще это очень удобно, ведь можно их заказывать готовые. Но, к сожалению, задержки будут гораздо больше: прохождение сигналов через триггеры, преобразование в код Грея и обратно — это довольно долго.

Ещё один интересный метод пересинхронизации я вычитал из статьи А.С Кожина, какую я укажу в источниках. Этот метод использовался в Эльбрус-C+, он предусматривает метки (сигналы) для высокочастотного домена. Причем для входа высокочастотного домена предусматривается метка clabel_i, служащая для того, чтобы высокочастотный домен не воспринимал одну посылку, как несколько (об этом было сказано, когда мы рассматривали синхронизаторы). Для выхода высокочастотного домена используется метка clabel_o, гарантирующая, что низкочастотный приемник примет данные (об этом тоже было сказано).

Здесь метка clabel_o разрешает изменение данных на выходе триггеров со стороны высокочастотного домена (обращайте внимание на data_out). На следующем фронте импульса приемника (приемник работает на частоте 2/5 Fsys), данные захватываются (это второй импульс 2/5 Fsys. Соотнесите его с data_out). Таким образом выполняется передача данных из высокочастотного домена в низкочастотный.

Здесь важно правильно формировать метки, чтобы соблюдались следующие требования: новые данные на data_out не должны захватываться предыдущим фронтом импульса (если бы первый импульс 2/5 Fsys захватил данные вместо второго), новые данные должны успеть переключиться до следующего фронта импульса (такое произошло, если бы второй импульс cabel_o появился позже).

Всё аналогично при передаче из низкочастотного домена в высокочастотный. Только в этому случае метка cabel_i обеспечивает выбор только одного фронта высокой частоты. Метки формируются в специальном блоке формирования меток.

Он состоит из регистра (такая память, состоящая из триггеров). Значение в регистре определяет, в какие такты периода биений (T align) разрешено выдавать метку. Период биений здесь, как вы можете посмотреть на предыдущем рисунке с меткой cabel_o — это период, при котором совпадают фронты импульсов. Ширина регистра определяется количеством тактовых импульсов за период биений (в Fsys было 5 таких). Основная метка выдается на частоте большего домена. Сигнал mode задает режим работы блоку формирования в зависимости от частот передающего и принимающего доменов. Указатель (Pointer) указывает на значение регистра, отвечающее за состояние метки (будет ли выдана или нет). Сигнал beat — это комбинационный сигнал биений, который определяет начало периода биений. Он помогает восстановить правильное значение указателя, если в нем изменился разряд.

Также синхронизация невозможна без самого блока пересинхронизации. Здесь всё стандартно, но всё-таки требуется раскрыть передачу из одного домена в другой, когда частоты доменов близки. Близкими частоты будут, если на низкочастотный импульс приходится один фронт высокочастотного домена или f1/f2 < 2 (где f1 >f2). Прием/передача могут быть невозможны из-за несоблюдения временнЫх интервалов. В этом случае используются триггеры, задерживающие на половину такта данные, и дополнительная метка, определяющая, когда задержанные данные можно использовать.

Подобный метод пересихронизации не так удобен и универсален, как асинхронный FIFO-буфер, но зато имеет меньшие задержки.

На этом всё. Спасибо за внимание, критикуйте, обсуждайте и задавайте вопросы.

Cortex-M7 — когда хочется большего.

В подавляющем количестве проектов возможностей предоставляемых вышеописанными ядрами достаточно, но случаются и исключения. Лично со мной такое случалось всего пару раз, причём лишь один раз по действительно уважительной причине — требовалась высокая производительность для подготовки данных для ASIC, контроллер Ethernet и шина CAN-FD c повышенной скоростью обмена.

Если на уровне универсальных микроконтроллеров с ядрами Cortex 4 и ниже, на мой субъективный взгляд, по параметру цена/функциональность сейчас лидирует фирма ST, то в области более высокопроизводительных чипов она уступает лидерство ATMEL, вернее, теперь уже недавно поглотившему его MICROCHIP. Поэтому я остановил свой выбор на серии ATSAMV71, стоимостью от 6 долларов.

Помимо вышеописанного (контроллер Ethernet и шина CAN-FD), по большому счёту, мы получаем, существенно увеличивающее производительность ядро с ускорителем операций, работающее на тактовой частоте до 300 МГц, интерфейсы для подключения видеоматрицы и поддержку динамической памяти.

В заключении попрошу имеющих опыт общения с микроконтроллерами попрошу выбрать подходящий ответ на вопрос.