Архитектура фон Неймана

Архитектура фон Неймана (von Neumann) — система принципов построения и функционирования компьютера, предложенная американским математиком Джоном фон Нейманом в 1945 году в статье «Предварительное рассмотрение логической конструкции электронно-вычислительного устройства». В соответствии с принципами фон Неймана компьютер состоит из арифметического логического устройства — АЛУ (англ. ALU, Arithmetic and Logic Unit), выполняющего арифметические и логические операции; устройства управления, предназначенного для организации выполнения программ; запоминающих устройств (ЗУ), в т.ч. оперативного запоминающего устройства (ОЗУ) и внешнего запоминающего устройства (ВЗУ); внешних устройств для ввода-вывода данных. Фон-неймановская архитектура компьютера считается классической, на ней построено большинство компьютеров. В общем случае, когда говорят об архитектуре фон Неймана, подразумевают физическое отделение процессорного модуля от устройств хранения программ и данных.

Первые компьютерные системы отличались жестко заданным набором исполняемых команд и программ. Примером такого рода вычислительных устройств являются калькуляторы. Идея хранения компьютерных программ в общей памяти позволяла превратить вычислительные машины в универсальные устройства, которые способны выполнять широкий круг задач.

Проект компьютера, хранящего свои программы в общей памяти, был разработан в середине 1940-х годов в Муровской школе электрических разработок (англ. The Moore School of Electrical Engineering) в Пенсильванского университете. Одним из авторов проекта был Джон фон Нейман. Предполагалось, что первой машиной, созданной по принципам архитектуры фон Неймана, станет машина «EDVAC», однако она увидела свет только в 1953 году. Другим разработчикам удалось создать вычислительные машины на основе архитектуры фон Неймана гораздо раньше: Марк I (Манчестерский университет, Великобритания, 21 июня 1948 года); EDSAC (Кембриджский университет, Великобритания, 6 мая 1949 года); BINAC (США, апрель-август 1949 года); CSIR Mk 1 (Австралия, ноябрь 1949 года); SEAC (США, 9 мая 1950 года).

Принципы Неймана-Лебедева

В каждой области науки и техники существуют фундаментальные идеи или принципы, определяющие на многие годы вперёд её содержание и направление развития. В компьютерных науках роль таких фундаментальных идей сыграли принципы, сформулированные независимо друг от друга двумя крупнейшими учёными XX века — Джоном фон Нейманом и Сергеем Алексеевичем Лебедевым.

Принципы Неймана-Лебедева — базовые принципы построения ЭВМ, сформулированные в середине прошлого века, не утратили свою актуальность и в наши дни.

Джон фон Нейман (1903-1957) — американский учёный, сделавший важный вклад в развитие целого ряда областей математики и физики. В 1946 г., анализируя сильные и слабые стороны ЭНИАКа, совместно с коллегами пришёл к идее нового типа организации ЭВМ.

Сергей Алексеевич Лебедев (1902-1974) — академик, основоположник вычислительной техники в СССР, главный конструктор первой отечественной электронной вычислительной машины МЭСМ, автор проектов компьютеров серии БЭСМ (Большая Электронная Счётная Машина), разработчик принципиальных положений суперкомпьютера «Эльбрус». В 1996 году посмертно награждён медалью «Пионер компьютерной техники» — самой престижной наградой международного компьютерного сообщества.

Рассмотрим сущность основных принципов Неймана-Лебедева:

Первый принцип определяет состав основных компонентов вычислительной машины.

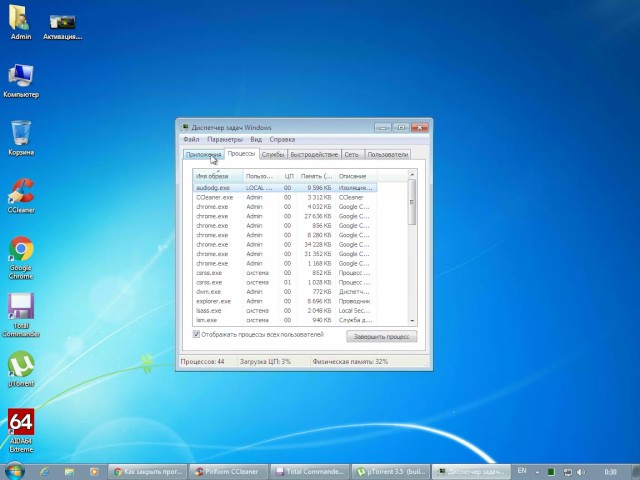

- все информационные потоки (тонкие стрелки на рисунке) проходят через процессор;

- управление всеми процессами (толстые стрелки на рисунке) также осуществляется процессором.

Рис. 2.5. Функциональная схема компьютеров первых поколений.

- процессор, состоящий из арифметико-логического устройства (АЛУ), выполняющего обработку данных, и устройства управления (УУ), обеспечивающего выполнение программы и организующего согласованное взаимодействие всех узлов компьютера;

- память, предназначенная для хранения исходных данных, промежуточных величин и результатов обработки информации, а также самой программы обработки информации. Различают память внутреннюю и внешнюю. Основная часть внутренней памяти используется для временного хранения программ и данных в процессе обработки. Такой вид памяти принято называть оперативным запоминающим устройством (ОЗУ). Ещё одним видом внутренней памяти является постоянное запоминающее устройство (ПЗУ), содержащее программу начальной загрузки компьютера. Внешняя или долговременная память предназначена для длительного хранения программ и данных в периоды между сеансами обработки;

- устройства ввода, преобразующие входную информацию в форму, доступную компьютеру;

- устройства вывода, преобразующие результаты работы компьютера в форму, доступную для восприятия человеком.

Вместе с тем в архитектуре современных компьютеров и компьютеров первых поколений есть существенные отличия. О них будет сказано чуть ниже.

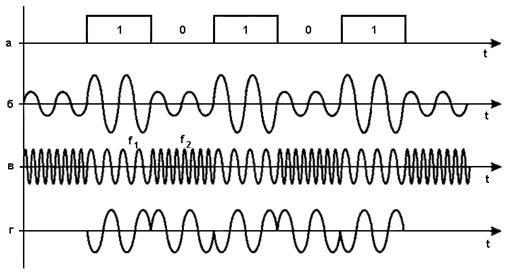

Рассмотрим суть принципа двоичного кодирования информации.

Все современные компьютеры хранят и обрабатывают информацию в двоичном коде. Выбор двоичной системы счисления обусловлен рядом важных обстоятельств: простотой выполнения арифметических операций в двоичной системе счисления, её «согласованностью» с булевой логикой, простотой технической реализации двоичного элемента памяти (триггера).

Структура ЭВМ по фон Нейману. Принципы фон Неймана

Первым теоретиком, сформулировавшим основы построения ЭВМ, был знаменитый математик Д. фон Нейман. В 1945 году он подготовил доклад, в котором ясно и просто описал общие принципы функционирования универсальных вычислительных устройств. Эти принципы используются до сих пор, они определяют структуру ЭВМ любого поколения. По мнению фон Неймана, ЭВМ состоит из:

1) Арифметико-логического устройства (АЛУ), предназначенного для выполнения арифметических и логических операций;

2) Устройства управления (УУ), организующего процесс выполнение программы;

3) Оперативно запоминающего устройства (ОЗУ), для хранения исходных данных и программ;

4) Внешнего устройства для ввода и вывода информации.

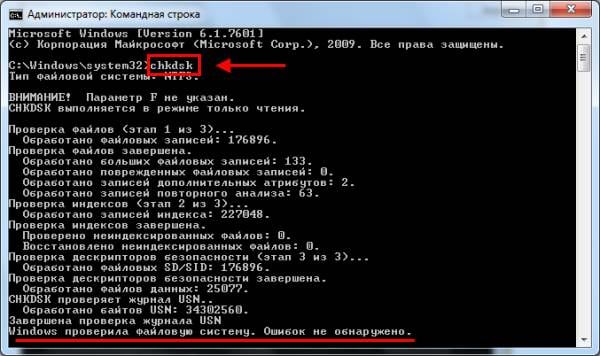

Рисунок: Стрелки указаны пути прохождения информации и управляющего сигнала. ОЗУ состоит из пронумерованных ячеек, в каждой из которых могут находиться или обрабатываться данные либо команды программы. Номер ячейки

называется адресом ячейки. Ячейка состоит из разрядов. В современных ЭВМ минимальной адресуемой единицей памяти служит 8 разрядная ячейка памяти – байт. Более крупные ячейки: 2-байтовые – полуслово, 4 – байтовые — слово, 8 – байтовые – двойное слово.

Первый принцип фон Неймана гласит, что все ячейки ОЗУ должны быть одинаково доступны для всех других устройств компьютера, т.е. время доступа для чтения или записи информации должно быть одинаково для всех ячеек памяти и не зависит от момента доступа. Этот принцип называют принципом произвольного доступа к основной памяти.

Второй принцип фон Неймана – принцип хранимой программы. Он гласит: программа, предназначенная для решения поставленной задачи, вводится в ОЗУ с внешнего устройства, и храниться в ней наряду с обрабатываемыми данными. Программа выполняется автоматически по сигналу из устройства управления. Этот принцип делает ЭВМ универсальным средством обработки информации, поскольку для решения новой задачи нужно ввести в память новую программу и соответствующие данные, а не перемонтировать электрические цепи, что делали в машине ENIAC.

Д. фон Нейман сформулировал и другие принципы работы ЭВМ. Например, дублирование важнейших электрических цепей и важнейших электрических цепей и важнейшей информации. Но именно выше описанные два принципа определяют архитектуру ЭВМ.

studopedia.org — Студопедия.Орг — 2014-2022 год. Студопедия не является автором материалов, которые размещены. Но предоставляет возможность бесплатного использования (0.011 с) .

Компьютеры, построенные на принципах фон Неймана

По плану, первым компьютером, построенным по архитектуре фон Неймана, должен был стать EDVAC (Electronic Discrete Variable Automatic Computer) — одна из первых электронных вычислительных машин. В отличие от своего предшественника ЭНИАКа, это был компьютер на двоичной, а не десятичной основе. Как и ЭНИАК, EDVAC был разработан в Институте Мура Пенсильванского Университета для Лаборатории баллистических исследований (англ.) Армии США командой инженеров и учёных во главе с Джоном Преспером Экертом (англ.) и Джоном Уильямом Мокли при активной помощи математика], однако до 1951 года EDVAC не был запущен из-за технических трудностей в создании надёжной компьютерной памяти и разногласий в группе разработчиков. Другие научно-исследовательские институты, ознакомившись с ЭНИАКом и проектом EDVAC, сумели решить эти проблемы гораздо раньше. Первыми компьютерами, в которых были реализованы основные особенности архитектуры фон Неймана, были:

- прототип — Манчестерская малая экспериментальная машина — Манчестерский университет, Великобритания, 21 июня 1948 года;

- EDSAC — Кембриджский университет, Великобритания, 6 мая 1949 года;

- Манчестерский Марк I — Манчестерский университет, Великобритания, 1949 год;

- BINAC — США, апрель или август 1949 года;

- CSIR Mk 1 — Австралия, ноябрь 1949 года;

- EDVAC — США, август 1949 года — фактически запущен в 1952 году;

- CSIRAC — Австралия, ноябрь 1949 года;

- SEAC — США, 9 мая 1950 года;

- ORDVAC — США, ноябрь 1951 года;

- IAS-машина — США, 10 июня 1952 года;

- MANIAC I — США, март 1952 года;

- AVIDAC — США, 28 января 1953 года;

- ORACLE — США, конец 1953 года;

- WEIZAC — Израиль, 1955 год;

- SILLIAC — Австралия, 4 июля 1956 года.

В СССР первой полностью электронной вычислительной машиной, близкой к принципам фон Неймана, стала МЭСМ, построенная Лебедевым (на базе киевского Института электротехники АН УССР), прошедшая государственные приемочные испытания в декабре 1951 года.

Узкое место архитектуры фон Неймана

Совместное использование шины для памяти программ и памяти данных приводит к узкому месту архитектуры фон Неймана, а именно ограничению пропускной способности между процессором и памятью по сравнению с объёмом памяти. Из-за того, что память программ и память данных не могут быть доступны в одно и то же время, пропускная способность канала «процессор-память» и скорость работы памяти существенно ограничивают скорость работы процессора — гораздо сильнее, чем если бы программы и данные хранились в разных местах. Так как скорость процессора и объём памяти увеличивались гораздо быстрее, чем пропускная способность между ними, узкое место стало большой проблемой, серьёзность которой возрастает с каждым новым поколением процессоров [источник не указан 1228 дней] ; данная проблема решается совершенствованием систем кэширования, а это порождает множество новых проблем.

Термин «узкое место архитектуры фон Неймана» ввел Джон Бэкус в 1977 в своей лекции «Можно ли освободить программирование от стиля фон Неймана?», которую он прочитал при вручении ему Премии Тьюринга [7] [8]

Ученые из США и Италии в 2015 заявили о создании прототипа мем-процессора (английское memprocessor) с отличной от фон-неймановской архитектурой и возможности его использования для решения NP-полных задач

CISC (англ. Complex instruction set computing, или англ. complex instruction set computer — компьютер с полным набором команд [1] ) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

- нефиксированное значение длины команды;

- арифметические действия кодируются в одной команде;

- небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Типичными представителями являются процессоры на основе команд x86 (исключая современные Intel Pentium 4, Pentium D, Core, AMD Athlon, Phenom, которые являются гибридными) и процессоры Motorola MC680x0.

Наиболее распространённая архитектура современных настольных, серверных и мобильных процессоров построена по архитектуре Intel x86 (или х86-64 в случае 64-разрядных процессоров). Формально, все х86-процессоры являлись CISC-процессорами, однако новые процессоры, начиная с Intel Pentium Pro, являются CISC-процессорами с RISC-ядром [2] . Они непосредственно перед исполнением преобразуют CISC-инструкции процессоров x86 в более простой набор внутренних инструкций RISC.

В микропроцессор встраивается аппаратный транслятор, превращающий команды x86 в команды внутреннего RISC-процессора. При этом одна команда x86 может порождать несколько RISC-команд (в случае процессоров типа P6 — до четырёх RISC-команд в большинстве случаев). Исполнение команд происходит на суперскалярном конвейере одновременно по несколько штук.

Это потребовалось для увеличения скорости обработки CISC-команд, так как известно, что любой CISC-процессор уступает RISC-процессорам по количеству выполняемых операций в секунду. В итоге, такой подход и позволил поднять производительность CPU.

Недостатки CISC архитектуры

- высокая стоимость аппаратной части;

- сложности с распараллеливанием вычислений.

Методика построения системы команд CISC противоположна другой методике — RISC. Различие этих концепций состоит в методах программирования, а не в реальной архитектуре процессора. Практически все современные процессоры эмулируют наборы команд как RISC-, так и CISC-типа.

В рабочих станциях, серверах среднего звена и персональных компьютерах используются процессоры с CISC. Наиболее распространенная архитектура команд процессоров мобильных устройств (SOC) и мэйнфреймов — RISC. В микроконтроллерах различных устройств RISC используется в подавляющем большинстве случаев.

RISC (англ. restricted (reduced) instruction set computer [1] [2] — «компьютер с сокращённым набором команд») — архитектура процессора, в котором быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. Первые RISC-процессоры даже не имели инструкций умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).

Наборы инструкций в более ранних архитектурах, для облегчения ручного написания программ на языках ассемблеров или прямо в машинных кодах, а также для упрощения реализации компиляторов, выполняли как можно больше работы. Нередко в наборы включались инструкции для прямой поддержки конструкций языков высокого уровня. Другая особенность этих наборов — большинство инструкций, как правило, допускали все возможные методы адресации (т. н. «ортогональность системы команд (англ.)») — к примеру, и операнды, и результат в арифметических операциях доступны не только в регистрах, но и через непосредственную адресацию, и прямо в памяти. Позднее такие архитектуры были названы CISC (англ. Complex instruction set computer).

Однако многие компиляторы не задействовали все возможности таких наборов инструкций, а на сложные методы адресации уходит много времени из-за дополнительных обращений к медленной памяти. Было показано, что такие функции лучше исполнять последовательностью более простых инструкций, если при этом процессор упрощается и в нём остаётся место для большего числа регистров, за счёт которых можно сократить количество обращений к памяти. В первых архитектурах, причисляемых к RISC, большинство инструкций для упрощения декодирования имеют одинаковую длину и похожую структуру, арифметические операции работают только с регистрами, а работа с памятью идёт через отдельные инструкции загрузки (load) и сохранения (store). Эти свойства и позволили лучше сбалансировать этапы конвейеризации, сделав конвейеры в RISC значительно более эффективными и позволив поднять тактовую частоту.

Философия RISC

В середине 1970-х разные исследователи (в частности, из IBM) показали, что большинство комбинаций инструкций и ортогональных методов адресации не использовались в большинстве программ, порождаемых компиляторами того времени. Также было обнаружено, что в некоторых архитектурах с микрокодной реализацией сложные операции зачастую были медленнее последовательности более простых операций, выполняющих те же действия. Это было вызвано, в частности, тем, что многие архитектуры разрабатывались в спешке и хорошо оптимизировался микрокод только тех инструкций, которые использовались чаще. [3]

Поскольку многие реальные программы тратят большинство своего времени на выполнение простых операций, многие исследователи решили сфокусироваться на том, чтобы сделать эти операции максимально быстрыми. Тактовая частота процессора ограничена временем, которое процессор тратит на выполнение наиболее медленных шагов в процессе обработки любой инструкции; уменьшение длительности таких шагов даёт общее повышение частоты, а также зачастую ускоряет выполнение и других инструкций за счёт более эффективной конвейеризации. [4] Фокусирование на простых инструкциях и ведёт к архитектуре RISC, цель которой — сделать инструкции настолько простыми, чтобы они легко конвейеризировались и тратили не более одного такта на каждом шаге конвейера на высоких частотах.

Позднее было отмечено, что наиболее значимая характеристика RISC в разделении инструкций для обработки данных и обращения к памяти — обращение к памяти идёт только через инструкции load и store, а все прочие инструкции ограничены внутренними регистрами. Это упростило архитектуру процессоров: позволило инструкциям иметь фиксированную длину, упростило конвейеры и изолировало логику, имеющую дело с задержками при доступе к памяти, только в двух инструкциях. В результате RISC-архитектуры стали называть также архитектурами load/store. [5]

Количество инструкций

Нередко слова «сокращённый набор команд» понимаются как минимизация количества инструкций в системе команд. В действительности, инструкций у многих RISC-процессоров больше, чем у CISC-процессоров. [6] [7] Некоторые RISC-процессоры вроде транспьютеров фирмы INMOS (англ.) имеют наборы команд не меньше, чем, например, у CISC-процессоров IBM System/370; и наоборот — CISC-процессор DEC PDP-8 имеет только 8 основных и несколько расширенных инструкций.

На самом деле, термин «сокращённый» в названии описывает тот факт, что сокращён объём (и время) работы, выполняемый каждой отдельной инструкцией — как максимум один цикл доступа к памяти, — тогда как сложные инструкции CISC-процессоров могут требовать сотен циклов доступа к памяти для своего выполнения. [8]

Некоторые архитектуры, специально разработанные для минимизации количества инструкций, сильно отличаются от классических RISC-архитектур и получили другие названия: Minimal instruction set computer (MISC), Zero instruction set computer (ZISC), Ultimate RISC (также называемый OISC), Transport triggered architecture (TTA) и т. п.

Следствия

Кроме того, архитектура Фоннеймановской машины обладает следующими особенностями:

1. Ячейки памяти имеют адреса, которые пронумерованы последовательно

Благодаря применению этого принципа стало возможным использование переменных в программировании. В частности, в любой момент можно обратиться к той или иной ячейке памяти по ее адресу.

2. Возможность условного перехода в ходе выполнения программы

Как уже было сказано, команды в программах должны выполняться последовательно. Однако предусмотрена возможность совершить переход к любому участку кода.

Архитектура вычислительных машин

Различают Принстонскую и Гарвардскую архитектуру вычислительных машин. Эти архитектурные варианты были предложены в конце 40-х годов специалистами, соответственно, Принстонского и Гарвардского университетов США для разрабатываемых ими моделей компьютеров.

Принстонская архитектура

Принстонская архитектура , которая часто называется архитектурой фон Неймана , характеризуется использованием общей оперативной памяти для хранения программ, данных, а также для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные.

Архитектура современных персональных компьютеров основана на

магистрально-модульном принципе .

Любую вычислительную машину образуют три основные компонента:

- процессор,

- память,

- устройства ввода-вывода (УВВ).

Информационная связь между устройствами компьютера осуществляется через системную шину (системную магистраль).

Шина – это кабель, состоящий из множества проводников. Количество проводников, входящих в состав шины, является

максимальной разрядностью шины .

Системная шина, в свою очередь, представляет собой совокупность

- шины данных, служащей для переноса информации;

- шины адреса, которая определяет, куда переносить информацию;

- шины управления, которая определяет правила для передачи информации;

- шины питания, подводящей электропитание ко всем узлам вычислительной машины.

Системная шина характеризуется тактовой частотой и разрядностью. Количество одновременно передаваемых по шине бит называется

разрядностью шины .

Тактовая частота характеризует число элементарных операций по передаче данных в 1 секунду. Разрядность шины измеряется в битах, тактовая частота – в мегагерцах.

Устройство управления (УУ) формирует адрес команды, которая должна быть выполнена в данном цикле, и выдает управляющий сигнал на чтение содержимого соответствующей ячейки запоминающего устройства (ЗУ). Считанная команда передается в УУ. По информации, содержащейся в адресных полях команды, УУ формирует адреса операндов и управляющие сигналы для их чтения из ЗУ и передачи в арифметико-логическое устройство (АЛУ). После считывания операндов устройство управления по коду операции, содержащемуся в команде, выдает в АЛУ сигналы на выполнение операции. Полученный результат записывается в ЗУ по адресу приемника результата под управлением сигналов записи. Признаки результата (знак, наличие переполнения, признак нуля и так далее) поступают в устройство управления, где записываются в специальный регистр признаков. Эта информация может использоваться при выполнении следующих команд программы, например команд условного перехода.

Устройство ввода позволяет ввести программу решения задачи и исходные данные в ЭВМ и поместить их в оперативную память. В зависимости от типа устройства ввода исходные данные для решения задачи вводятся непосредственно с клавиатуры, либо они должны быть предварительно помещены на какой-либо носитель (дисковый накопитель).

Устройство вывода служит для вывода из ЭВМ результатов обработки исходной информации. Чаще всего это символьная информация, которая выводится с помощью печатающих устройств или на экран дисплея.

Запоминающее устройство или память – это совокупность ячеек, предназначенных для хранения некоторого кода. Каждой из ячеек присвоен свой номер, называемый адресом . Информацией, записанной в ячейке, могут быть как команды в машинном виде, так и данные.

Обработка данных и команд осуществляется посредством арифметико-логического устройства (АЛУ), предназначенного для непосредственного выполнения машинных команд под действием устройства управления. АЛУ и УУ совместно образуют центральное процессорное устройство (ЦПУ). Результаты обработки передаются в память.

Основные принципы построения вычислительных машин с архитектурой фон Неймана

- Принцип двоичности. Для представления данных и команд используется двоичная система счисления.

- Принцип программного управления. Программа состоит из набора команд, которые выполняются процессором друг за другом в определённой последовательности.

- Принцип однородности памяти. Как программы (команды), так и данные хранятся в одной и той же памяти (и кодируются в одной и той же системе счисления, чаще всего – двоичной). Над командами можно выполнять такие же действия, как и над данными.

- Принцип адресуемости памяти. Структурно основная память состоит из пронумерованных ячеек, процессору в произвольный момент времени доступна любая ячейка.

- Принцип последовательного программного управления. Все команды располагаются в памяти и выполняются последовательно, одна после завершения другой.

- Принцип условного перехода. Команды из программы не всегда выполняются одна за другой. Возможно присутствие в программе команд условного перехода (а также команд вызова функций и обработки прерываний), которые изменяют последовательность выполнения команд в зависимости от значений данных. Этот принцип был сформулирован задолго до фон Неймана Адой Лавлейс и Чарльзом Бэббиджем, однако был логически включен в указанный набор как дополняющий предыдущий принцип.

Архитектура фон Неймана имеет ряд важных достоинств.

- Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач. Таким образом, обеспечивается возможность более эффективного использования имеющегося объема оперативной памяти в каждом конкретном случае применения.

- Использование общей шины для передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность.

Поэтому Принстонская архитектура в течение долгого времени доминировала в вычислительной технике.

Однако ей присущи и существенные недостатки. Основным из них является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится «узким местом» (bottleneck – «бутылочное горло»), которое ограничивает производительность цифровой системы.

Гарвардская архитектура

Гарвардская архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете с целью увеличить скорость выполнения вычислительных операций и оптимизировать работу памяти. Она характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры.

Недостатки Гарвардской архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходится использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки, поэтому Гарвардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, где используется отдельная кэш-память для хранения команд и данных. В то же время во внешней структуре большинства микропроцессорных систем реализуются принципы Принстонской архитектуры.