Что такое архитектура компьютера

Архитектура персонального компьютера (ПК) включает в себя структуру, которая отражает состав ПК, и программное обеспечение.

Структура ПК – это набор его функциональных элементов (от основных логических узлов до простейших схем) и связей между ними.

Архитектура определяет принципы действия, информационные связи и взаимное соединение основных логических узлов ПК, к которым относят процессор, оперативное запоминающее устройство, внешние запоминающие устройства и периферийные устройства.

Основным принципом построения всех современных ПК является программное управление.

Классическая архитектура фон Неймана

В $1946$ году американские математики Джон фон Нейман, Герман Голдштейн и Артур Бёркс в совместной статье изложили новые принципы построения и функционирования ЭВМ. На основе этих принципов производилось $1$-е и $2$-е поколение компьютеров. В следующих поколениях происходили некоторые изменения, но принципы фон Неймана (как они были названы) сохранялись.

Основные принципы фон Неймана:

- Использование двоичной системы счисления в ПК, в которой устройствам гораздо проще выполнять арифметико-логические операции, чем в десятичной.

- Программное управление ПК. Работа ПК управляется программой, которая состоит из набора команд, выполняющихся последовательно одна за другой. Создание машины с хранимой в памяти программой положило начало программированию.

- Данные и программы хранятся в памяти ПК. Команды и данные кодируются одинаково в двоичной системе.

- Ячейки памяти ПК имеют последовательно пронумерованные адреса. Возможность обращения к любой ячейке памяти по ее адресу позволила использовать переменные в программировании.

- Возможность условного перехода при выполнении программы. Команды в ПК выполняются последовательно, но при необходимости можно реализовать переход к любой части кода.

Основным принципом было то, что программа уже стала не постоянной частью машины, а изменяемой, в отличие от аппаратуры, которая остается неизменной и очень простой.

Фон Нейманом также была предложена структура ПК (рис. 1).

Рисунок 1. Структура ПК

В состав машины фон Неймана входили:

- запоминающее устройство (ЗУ);

- арифметико-логическое устройство (АЛУ), которое выполняло все арифметические и логические операции;

- устройство управления (УУ), которое координирует действия всех узлов машины в соответствии с программой;

- устройства ввода-вывода.

Программы и данные вводились в ЗУ из устройства ввода через АЛУ. Все команды программы записывались в ячейки памяти последовательно, а данные для обработки – в произвольные ячейки.

Команда состояла из указания операции, которую необходимо выполнить, и адресов ячеек памяти, в которых хранятся данные и над которыми необходимо выполнить нужную операцию, а также адреса ячейки, в которую необходимо записать результат (для хранения в ЗУ).

Из АЛУ результаты выводятся в ЗУ или устройство вывода. Принципиально эти устройства отличаются тем, что в ЗУ данные хранятся в удобном для обработки ПК виде, а на устройства вывода (монитор, принтер и т.п.) в удобном для человека.

От УУ на другие устройства поступают сигналы с командами, а от других устройств УУ получает информацию о результате их выполнения.

В УУ содержится специальный регистр (ячейка) – счетчик команд, в который записывается адрес первой команды программы. УУ считывает из памяти содержимое соответствующей ячейки памяти и помещает его в специальное устройство – регистр команд. УУ определяет операцию команды, «отмечает» в памяти данные, адреса которых указаны в команде, и контролирует выполнение команды. Операцию выполняет АЛУ или аппаратные средства компьютера.

После выполнения команды счетчик команд увеличивается на $1$ и указывает на следующую команду программы. При необходимости выполнения команды, которая не следует по порядку за текущей, специальная команда перехода содержит адрес ячейки, в которую нужно передать управление.

Архитектура современных ПК

В основу архитектуры современных ПК заложен магистрально-модульный принцип. ПК состоит из отдельных частей – модулей, которые являются относительно самостоятельными устройствами ПК (напрмер, процессор, оперативная память, контроллер, дисплей, принтер, сканер и т.д.).

Модульный принцип позволяет пользователю самостоятельно комплектовать необходимую конфигурацию ПК и производить при необходимости его обновление. Модульная организация системы опирается на магистральный принцип обмена информацией. Для работы ПК как единого механизма необходимо осуществлять обмен данными между различными устройствами, за что отвечает системная (магистральная) шина, которая выполняется в виде печатного мостика на материнской плате.

Основные особенности архитектуры ПК сводятся к принципам компоновки аппаратуры, а также к выбранному набору системных аппаратных средств.

Подобная архитектура характеризуется ее открытостью – возможностью включения в ПК дополнительных устройств (системных и периферийных), а также возможностью простого встраивания программ пользователя на любом уровне программного обеспечения ПК.

Также совершенствование архитектуры ПК связано с максимальным ускорением обмена информацией с системной памятью. Именно из системной памяти, в которой хранятся данные, ПК считывает все исполняемые команды. Таким образом больше всего обращений центральный процессор совершает к памяти и ускорение обмена с памятью приведет к существенному ускорению работы всей системы в целом.

Т.к. при использовании системной магистрали для обмена процессора с памятью приходится учитывать скоростные ограничения самой магистрали, то существенного ускорения обмена данными с помощью магистрали добиться невозможно.

Для решения этого вопроса был предложен следующий подход. Системная память вместо системной магистрали подключается к специальной высокоскоростной шине, которая дистанционно находится ближе к процессору и не требует сложных буферов и больших расстояний. В этом случае обмен с памятью идет с максимально возможной для процессора скоростью, и системная магистраль не замедляет его. Особенно актуальным это решение стало с ростом быстродействия процессора.

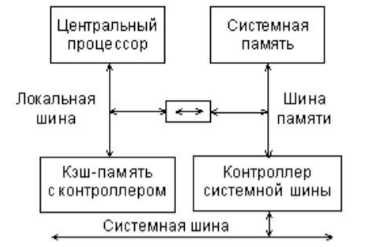

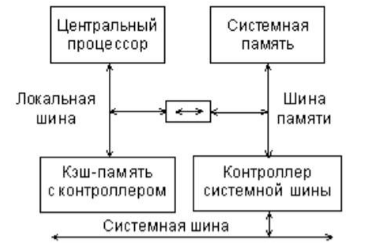

Таким образом, структура ПК из одношинной, которая применялась только в первых компьютерах, становится трехшинной.

Рисунок 2. Трехшинная структура ПК

АЛУ и УУ в современных ПК образуют процессор. Процессор, который состоит из одной или нескольких больших интегральных схем, называется микропроцессором или микропроцессорным комплектом.

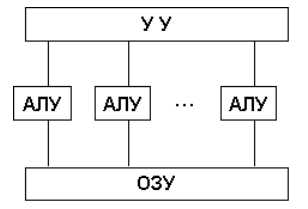

Многопроцессорная архитектура ПК

Наличие в ПК нескольких процессоров означает, что параллельно может быть организовано много потоков данных и команд, т.е. одновременно могут выполняться несколько фрагментов одной задачи.

Рисунок 3. Архитектура многопроцессорного ПК

Многомашинная вычислительная система

В архитектуре многомашинной вычислительной системы каждый процессор имеет свою оперативную память. Применение многомашинной вычислительной системы эффективно при решении задач, которые имеют очень специальную структуру, которая должна состоять из такого количества ПК, на сколько слабо связанных подзадач разбита система.

Многопроцессорные и многомашинные вычислительные системы имеют преимущество перед однопроцессорными в быстродействии.

Архитектура с параллельными процессорами

В данной архитектуре несколько АЛУ работают под управлением одного УУ. Это означает, что множество данных может обрабатываться по одной программе, т. е. по одному потоку команд. Высокое быстродействие такой архитектуры можно получить только на задачах, в которых одинаковые вычислительные операции выполняются одновременно на различных однотипных наборах данных.

Рисунок 4. Архитектура с параллельным процессором

В современных машинах часто присутствуют элементы различных типов архитектурных решений. Существуют и другие архитектурные решения, отличные от рассмотренных выше.

Классическая архитектура компьютера

Ключевые принципы, в соответствии с которыми предполагалось конструирование ПК по определенной логической схеме, предложил Джон фон Нейман, выдающийся математик. Его идеи были реализованы производителями ПК, относящихся к первым двум поколениям. Концепция, разработанная Джоном фон Нейманом, — это классическая архитектура ПК. Каковы ее особенности? Предполагается, что компьютер должен состоять из следующих основных компонентов:

— арифметического и логического блока;

— устройства для управления;

— блока внешней памяти;

— блока оперативной памяти;

— устройств, предназначенных для ввода и вывода информации.

В рамках данной схемы взаимодействие технологических компонентов должно реализовываться по конкретной последовательности. Так, сначала в память ПК попадают данные из компьютерной программы, которые могут вводиться с помощью внешнего устройства. Затем устройство для управления считывает информацию из памяти компьютера, после чего направляет ее на выполнение. В этом процессе при необходимости задействуются остальные компоненты ПК.

Архитектура современных ПК

В основу архитектуры современных ПК заложен магистрально-модульный принцип. ПК состоит из отдельных частей – модулей, которые являются относительно самостоятельными устройствами ПК (напрмер, процессор, оперативная память, контроллер, дисплей, принтер, сканер и т.д.).

Модульный принцип позволяет пользователю самостоятельно комплектовать необходимую конфигурацию ПК и производить при необходимости его обновление. Модульная организация системы опирается на магистральный принцип обмена информацией. Для работы ПК как единого механизма необходимо осуществлять обмен данными между различными устройствами, за что отвечает системная (магистральная) шина, которая выполняется в виде печатного мостика на материнской плате.

Основные особенности архитектуры ПК сводятся к принципам компоновки аппаратуры, а также к выбранному набору системных аппаратных средств.

Подобная архитектура характеризуется ее открытостью – возможностью включения в ПК дополнительных устройств (системных и периферийных), а также возможностью простого встраивания программ пользователя на любом уровне программного обеспечения ПК.

Также совершенствование архитектуры ПК связано с максимальным ускорением обмена информацией с системной памятью. Именно из системной памяти, в которой хранятся данные, ПК считывает все исполняемые команды. Таким образом больше всего обращений центральный процессор совершает к памяти и ускорение обмена с памятью приведет к существенному ускорению работы всей системы в целом.

Т.к. при использовании системной магистрали для обмена процессора с памятью приходится учитывать скоростные ограничения самой магистрали, то существенного ускорения обмена данными с помощью магистрали добиться невозможно.

Для решения этого вопроса был предложен следующий подход. Системная память вместо системной магистрали подключается к специальной высокоскоростной шине, которая дистанционно находится ближе к процессору и не требует сложных буферов и больших расстояний. В этом случае обмен с памятью идет с максимально возможной для процессора скоростью, и системная магистраль не замедляет его. Особенно актуальным это решение стало с ростом быстродействия процессора.

Таким образом, структура ПК из одношинной, которая применялась только в первых компьютерах, становится трехшинной.

Рисунок 2. Трехшинная структура ПК

АЛУ и УУ в современных ПК образуют процессор. Процессор, который состоит из одной или нескольких больших интегральных схем, называется микропроцессором или микропроцессорным комплектом.

Логические схемы

Логическая схема — это набор объединенных вентилей с входными и выходными сигналами. На рис 1.1 тоже изображена схема у которой входными сигналами являются A и B, выходной сигнал идет от операции ИЛИ; также у нее есть три вентиля: два И, один ИЛИ. Теперь давайте рассмотрим некоторые виды схем с которыми нам потребуется встречаться в дальнейшем, к ним относятся: комбинационные, арифметические, интегральные схемы.

Комбинационные схемы

Комбинационная схема — это схема с одним дополнительным свойством: значения выходных сигналов зависят только от входных, или другими словами, в ней нет никаких запоминающих устройств. Из этого вида схем создаются переиспользуемые компоненты, которые применяются для реализации большинства других схем, мы рассмотрим несколько, а именно: компаратор, декодер, мультиплексор/демультиплексор.

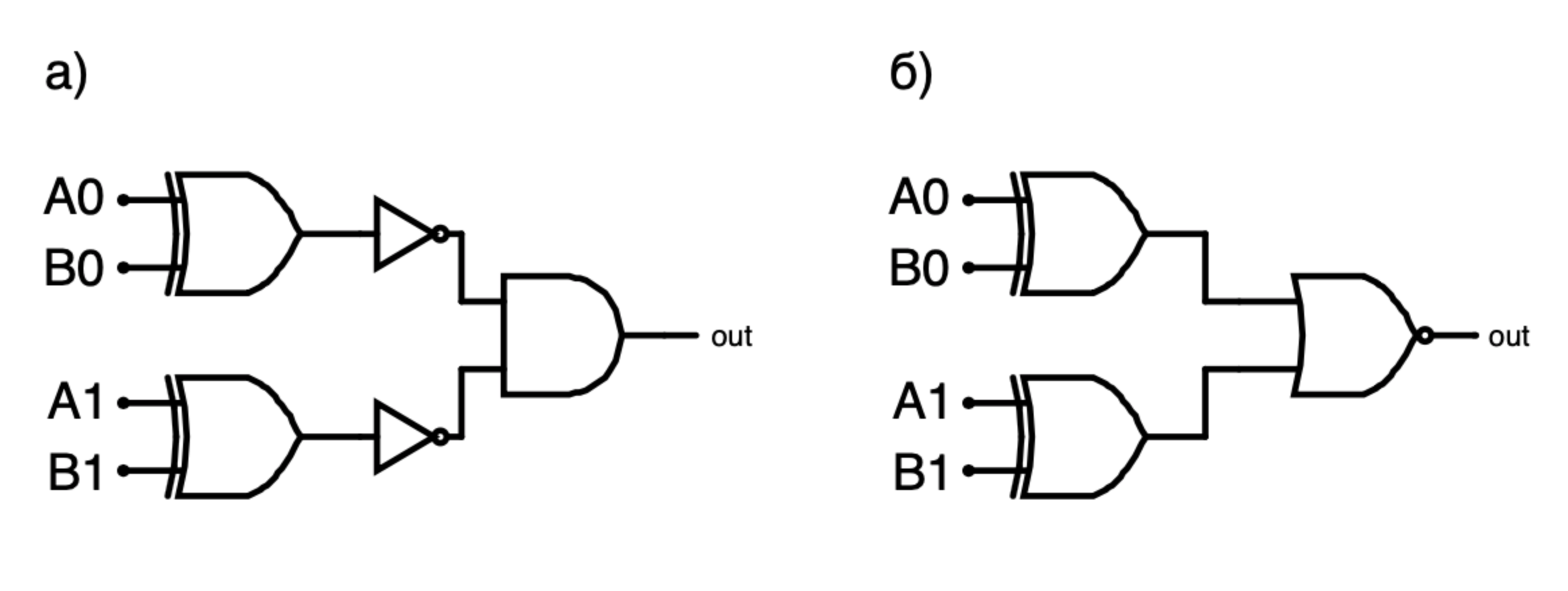

Компаратор имеет n входных парных линий (то есть 2n входов) и одну выходную линию. Логика его работы заключается в том, чтобы сравнить каждую пару битов (биты слова A сравниваются с соответствующими битами слова B) и при неравенстве хоть одной из них выдать 0 (если за ложь принят 0), иначе 1. Давайте построим таблицу истинности (табл. 1.1) для однобитного компаратора; можно заметить, что она равна таблице истинности ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (когда к операции добавлен НЕ, то все выходные значения в таблице становятся противоположными). Теперь давайте расширим его до двухбитного компаратора, построим таблицу истинности (табл. 1.2) для него от двух переменных значения которых зависит от двух однобитных компаратора, то есть от двух ИСКЛЮЧАЮЩЕГО ИЛИ-НЕ; в ней значение 1 в CMP0 (и CMP1) значит, что два входа какото-то компаратора равны, 0 наоборот, то есть 1 в столбце R должна быть только, когда значения равны в двух компараторах. Эта таблица истинности совпадает с таблицей И, то есть мы объединяем все ИСКЛЮЧАЮЩЕГО ИЛИ-НЕ операцией И и у нас получится двухбитный компаратор (рис. 1.3а). Для дальнейшего расширение компаратора необходимо лишь добавить ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и подсоединить его к И. Недостаток такой реализации заключается в ее избыточности, нам требуется добавлять вентили НЕ для каждого ИСКЛЮЧАЮЩЕГО ИЛИ; мы можем от этого избавится (рис. 1.3б), если заменим вентиль И с НЕ входами на ИЛИ-НЕ, так как их таблицы истинности совпадают.

Таблица. 1.1. Таблица истинности для однобитного компаратора.

| A | B | CMP |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| CMP0 | CMP1 | R |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Рисунок 1.3. Две схемы двухбитных компараторов.

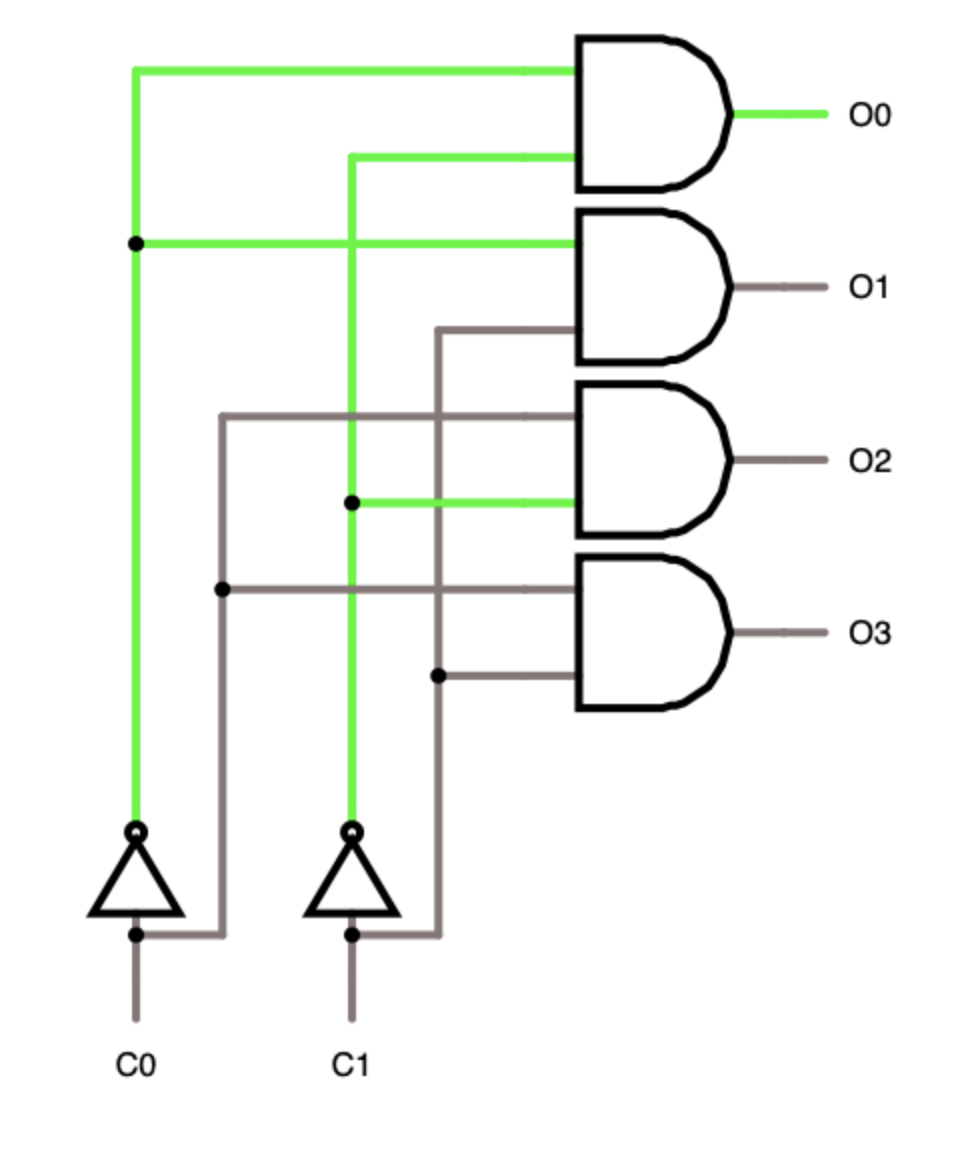

Декодер обладает n входными линиями, 2^n выходными, он реализован так, чтобы сигнал (истинна, 1) прошел только в одну выходную линию. Каждый выходной вентиль И получает свою комбинацию значений переменных, которые (значения) находятся в какой-то строке таблицы истинности, а как мы уже знаем, строку таблицы истинности можно реализовать как минтерму, то есть мы каждую строку представляем как вентиль И (рис. 1.4) от нескольких переменных. Основное применение декодера заключается в выборочном включении разных частей схемы (или схем), например, у АЛУ (о нем далее) имеется несколько операции, которые он может выполнять над входными значениями, чтобы их выбрать одну из них используется декодер.

Рисунок 1.4 Декодер.

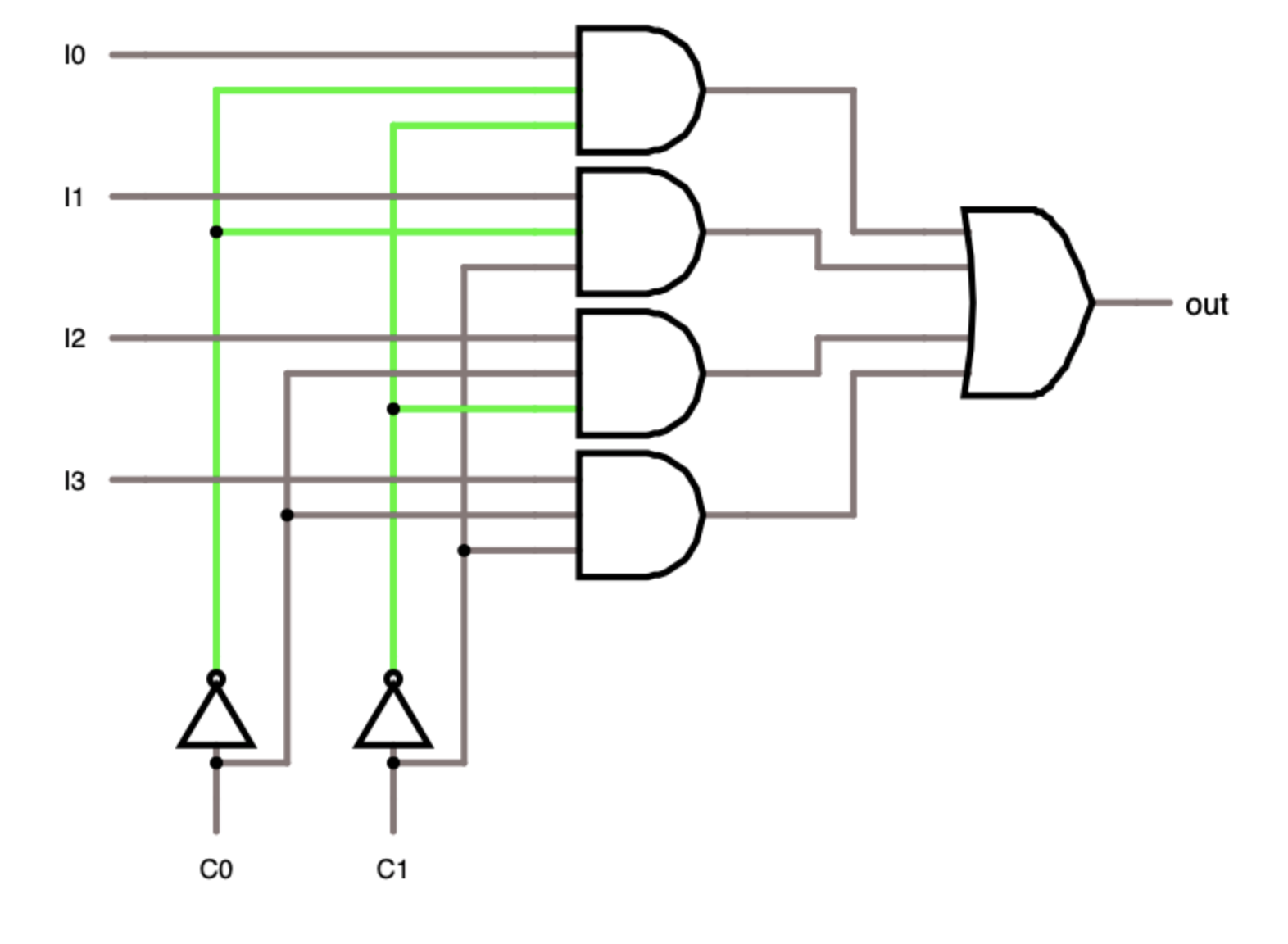

Мультиплексор/демультиплексор

Мультиплексор обладает 2^n входными линиями, n линиями управления и одной выходной линией. Он в реализации в какой-то степени похож (рис 1.5) на декодер, если представить входы декодера как линии управления, дополнить каждый вентиль И дополнительным входным сигналом и объединить выходные значения всех И одним ИЛИ. Суть его работы заключается в том, чтобы на выход поступал сигнал только от одной из возможных входных линий. Мультиплексор применяется в разных целях, например, он может пригодиться для преобразования параллельного кода в последовательный. Допустим у нас есть параллельная (это значит, что линии работают одновременно) шина с несколькими линиями по которым параллельно передаются биты; чтобы считать нужное нам слово (обычно разрядность слова соответствует разрядности регистра в процессоре) мы соединяем линий шины с входами мультиплексора и последовательно включаем по одному входу, допустим сверху вниз, тем самым на выход у нас пойдет точная последовательность битов.

Демультиплексор является обратным мультиплексору, он имеет одну входную линию, n линий управления и 2^n выходных линий. Логика его работы точно такая же как и в мультиплексоре, только один входной сигнал идет в один из выходных. Может быть использован для преобразования последовательного кода в параллельный.

Рисунок 1.5. Мультиплексор.

Арифметические схема

Данный вид схем выполняет арифметические операции над входными сигналами. Основными схемами являются: логические функции, сумматор, схема сдвига, АЛУ (ALU, Arithmetic Logic Unit).

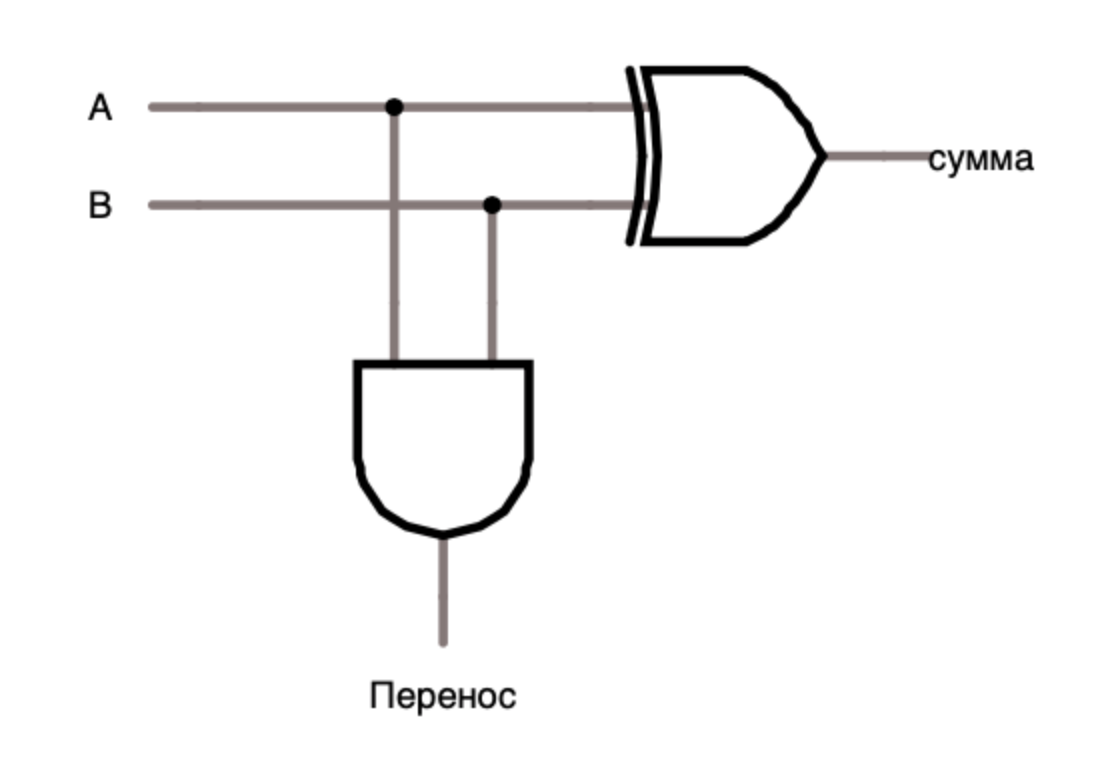

Полусумматор и полный сумматор

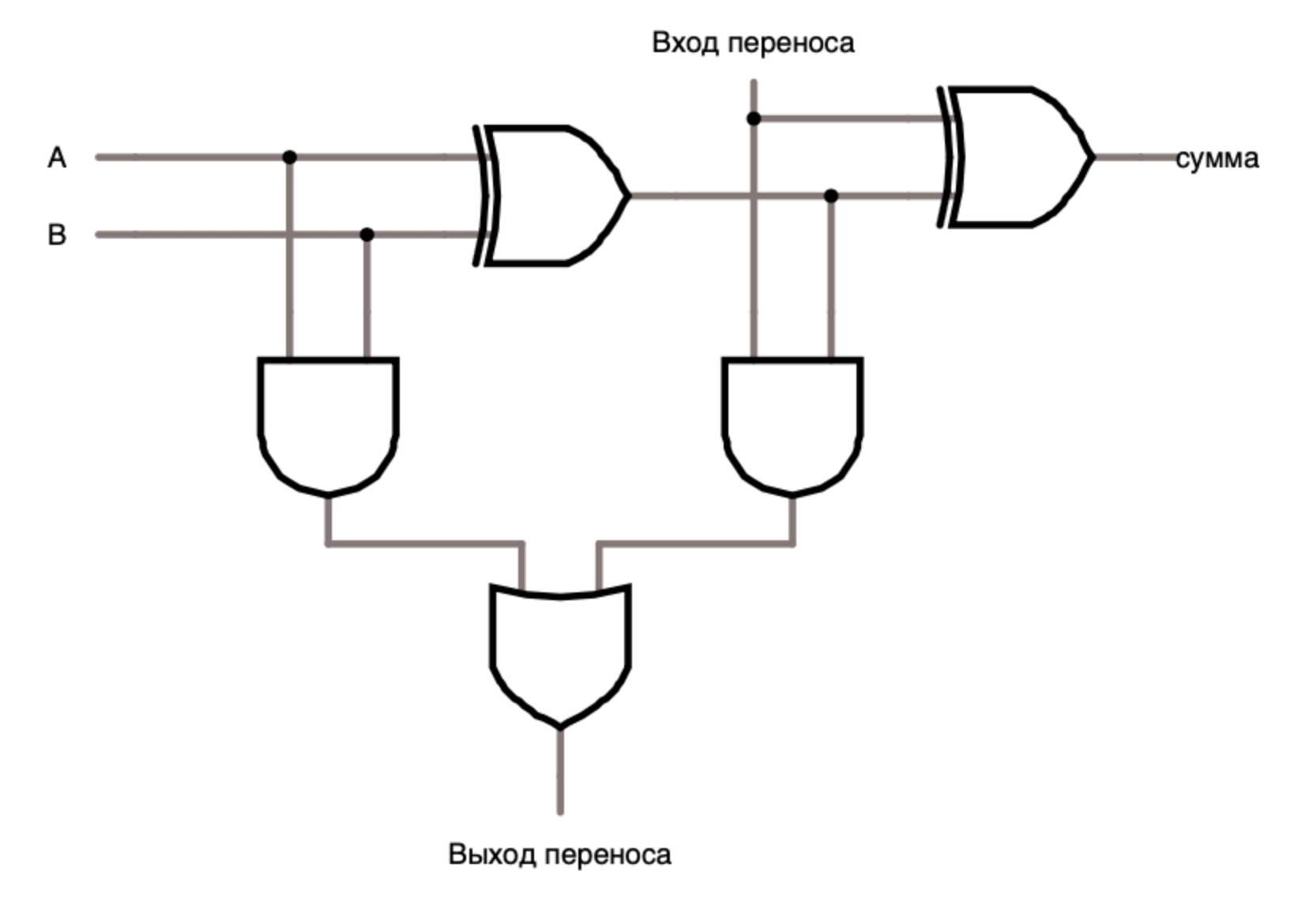

Полусумматор состоит из двух входных и двух выходных линий, Полусумматор является простой схемой (рис. 1.6) из двух вентилей: И и ИСКЛЮЧАЮЩЕЕ ИЛИ. Сам по себе полусумматор может складывать только одноразрядные значения, но зачем же тогда нам нужен полный сумматор? В основном мы хотим складывать значения с большей разрядностью, но только одним полусумматором мы удовлетворить это желание не может. Когда мы складываем два одноразрядных значения, то у нас может произойти переполнение (табл. 1.3 последняя строка истинности в столбике перенос). Это когда результат операции не помещается в той разрядности, которой обладают входные элементы (в данном случае 1). При сложении двух единиц получает двойка, которую нельзя сохранить в одном бите, поэтому необходимо перенести его, чтобы воспользоваться при дальнейших вычислениях, но так как в полусумматоре не предусмотрена возможность использования двух значений и переноса одновременно, то складывать значения с разрядностью более чем единицу не получится. Например, допустим мы складываем два 3-разрядных числа, 5 (101 в двоичной) и 7 (111 в двоичной), сложение двух чисел начинается с младших разрядов, на входы полусумматора направляются 1 и 1, на выходе суммы получаем 0 и на выходе переноса 1, вот здесь и возникает проблема, следующие значения, которые должны пойти в полусумматор, это 0 и 1 соответственно, но, что делать с переносом, ведь для него нет никакого свободного входа, а отбросить его нельзя, поэтому полусумматоры не могут напрямую использоваться для сложений.

У полного сумматора есть (рис. 1.7) три входных линии и две выходные линии. Входной перенос, как и выходной, используется для возможности объединения сумматоров в один с большей разрядностью. Сумматор состоит из двух полусумматоров, чтобы построить сумматор большей разрядности, необходимо только объединить сумматоры через входные и выходные переносы.

Рисунок 1.6. Схема полусумматор.

Таблица 1.3. Таблица истинности полусумматора.

| A | B | Сумма | Перенос |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Рисунок 1.7. Схема полного сумматора.

Таблица 1.4. Таблица истинности полного сумматора.

| A | B | Вход перенос | Сумма | Выход перенос |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

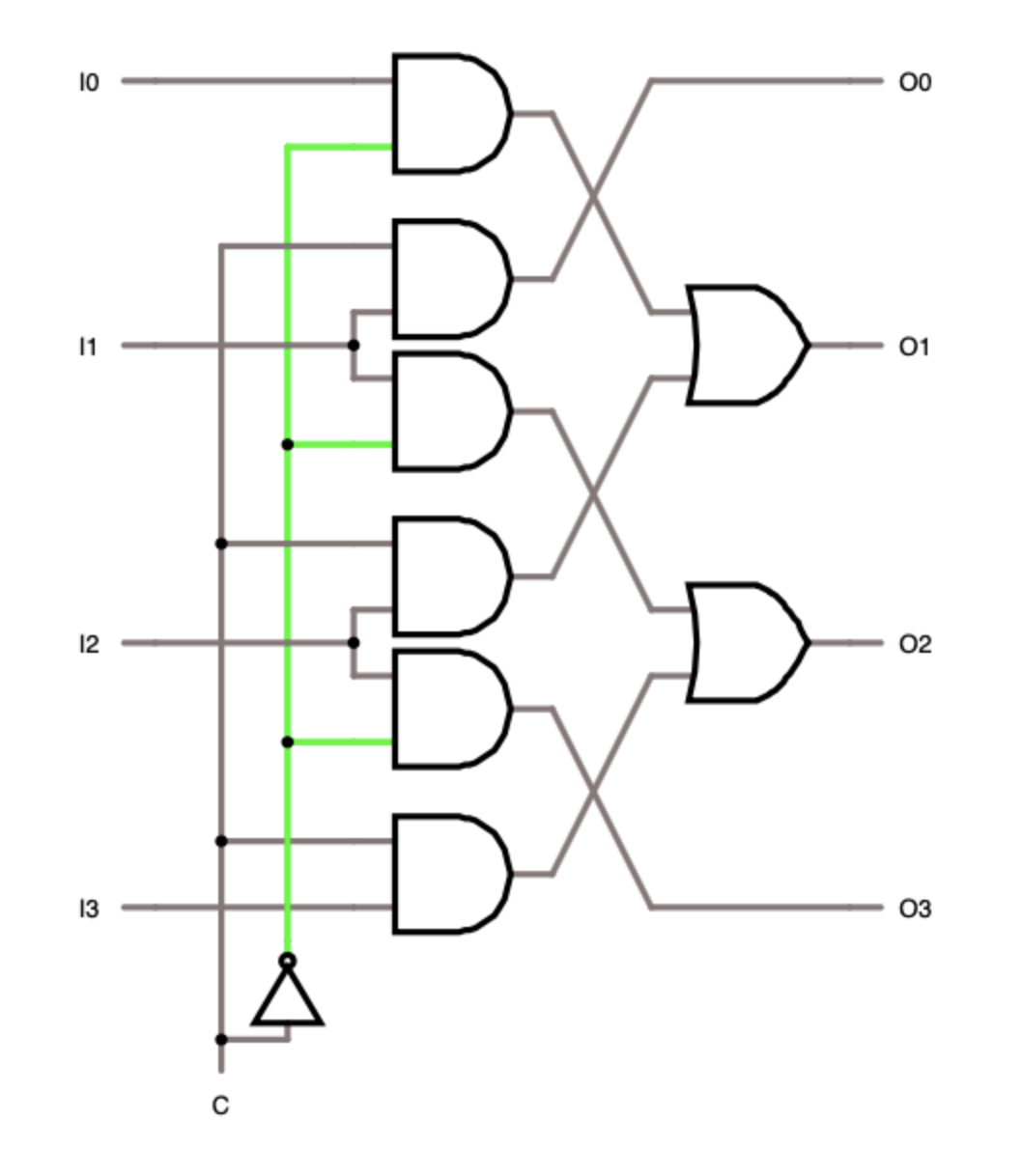

Схема сдвига

Сдвиг необходим для того, чтобы, например, выполнять умножение (сдвиг влево) и деление (сдвиг вправо), но только с числами, которые являются степенью двойки (1, 2, 4, 8 и тд). Схема сдвига (рис. 1.8) должна выполнять смещение на одну позицию влево или вправо в зависимости от бита направления. Бит направления (С) в зависимости от своего значения включает те или иные вентили И. Если он равен 0 (сдвиг влево), то сигнал который идет напрямую (то есть не проходит через НЕ) будет выключать вентиль который находятся выше в паре из двух вентилей И и один крайний вентиль И снизу. Сигнал, который проходит через НЕ, будет включать нижние вентиль в паре из двух вентилей И и один крайний вентиль И сверху. Это значит, что входные значения In будут выходить только из вентилей И выходные сигналы, которых направлены в нижнюю сторону; старший бит (I3) будет утерян, так как самый нижний вентиль И не пропустит входной сигнал дальше. Аналогичная ситуация происходит, когда бит направления равен 1 (сдвиг вправо), только теперь будут включены другие вентили И и сигнал уже будет направлен в противоположную (в данной реализации) сторону, и, следовательно, произойдет сдвиг вправо.

Рисунок 1.8. Схема сдвига.

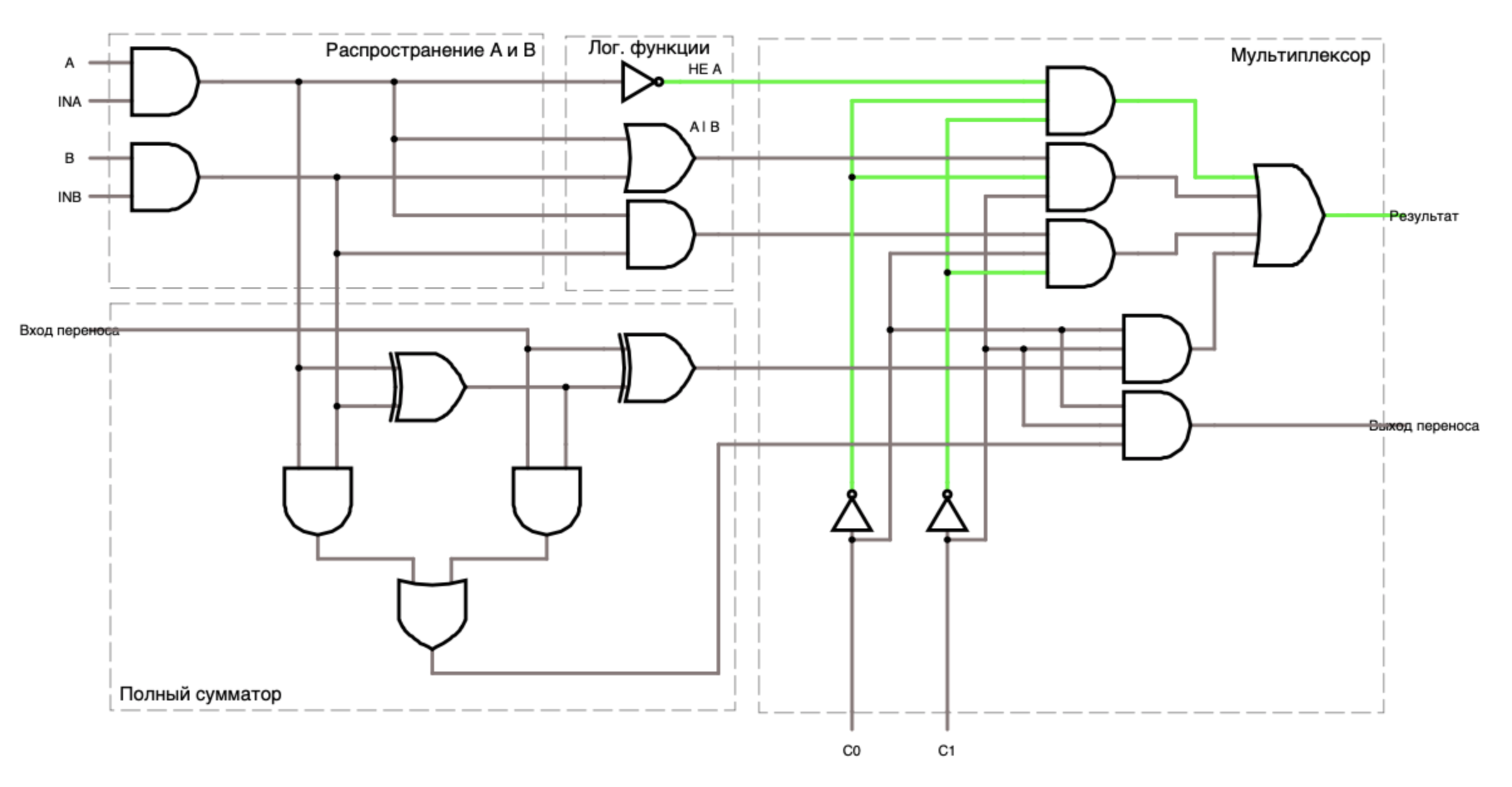

Арифметико Логическое Устройство

АЛУ — это схема (рис. 1.9), которая содержит в себе множество арифметических схем, она предназначена для того, чтобы в одном месте хранить все операции необходимые для какой-либо цели. Реализация АЛУ разделяется на несколько частей (в данной реализации): распространение входных операндов, логические функции, сумматор и мультиплексор. Как мы помним декодер должен выполнять«включение» операций, но здесь я решил сделать мультиплексор, который подает на выход «Результат» значение, только одной из четырех операций; два нижних вентиля И в нем делят одну и ту же комбинацию при которой мультиплексор работает, это необходимо потому, что «Выход переноса» и «Сумма» сумматора являются частью одной операции, то есть оба этих входа должны работать только когда выбрано суммирование. Наш АЛУ предназначен для работы с одноразрядными значениями, но его можно почти без проблем изменить на большую разрядность. Входные линии INA и INB предназначены для включения/выключения A и B соответственно.

Рисунок 1.9. Схема АЛУ.

Интегральные схемы

Также известна как микросхема, это те же схемы показанные выше, только они помещены в корпус, который определяет, то где должны находится выводы для сигналов. Этот вид схем возник из-за того, что продавать отдельные схемы и вентили не очень целесообразно: по крайне мере из-за того, что нет стандарта, который бы говорил как, где и в каком кол-ве должны располагаться входные и выходные сигналы.

Есть куча разных видов корпусов, но мы рассмотрим наиболее известные:

- Dual Inline Package (DIP) представляет собой корпус (рис. 2.0а) у которого выводы (входные и выходные сигналы) расположены с двух сторон параллельных друг другу, кол-во выводов в данном корпусе варьируется в пределах от 14 до 68 (только четное кол-во). Данный корпус используется при небольших и/или дешевых схемах.

- Pin Grid Array (PGA) обладает выводами со всех четырех сторон (рис. 2.0б).

- Land Grid Array (LGA) обладает выводами в виде контактов по всей (зависит от стандарта) площадке (нижняя часть) корпуса. LGA (рис. 2.0в) обладает одним важным преимуществом перед другими корпусами: большое кол-во выводов, что особенно важно для таких микросхем как процессоры.