Rеволюционный DMA: быстрее, чем TCP

Можно ли обеспечить рост мощностей серверной инфраструктуры (вычислений и хранения) без привлечения сетевых архитектур SAN, специализированных устройств хранения и протоколов передачи данных, висящих тяжелыми гирями на пользователе, его кошельке и степенях его свободы? Берем привычную среду связи серверов и систем хранения на классических сетевых протоколах TCP. Она не идеальна, но доступна, универсальна и перспективна. Оказывается, давно и хорошо знакомое понятие DMA (Direct Memory Access) можно распространить на совокупность контроллеров NIC (Network Interface Controller) нескольких компьютеров, соединенных в локальную сеть.

Интеллектуальный транс-платформенный контроллер DMA при соответствующей программной поддержке обобщает и унифицирует понятие прямого доступа к памяти. Единый подход для доступа в адресное пространство как локального, так и удаленного компьютера обозначили термином RDMA (Remote Direct Memory Access).

В прикладном смысле RDMA — это механизм передачи данных между локальной сетью и оперативной памятью вычислительной платформы. Унифицируется вся адресация — и привилегированной памяти операционной системы, и виртуальной памяти, принадлежащей приложениям. Таким образом, два приложения, запущенные на различных платформах, могут взаимодействовать посредством почти общей памяти. Вообще же, термину RDMA — как спутнику передачи данных без участия центрального процессора — несколько десятков лет. Теперь восходящая спираль технологий достала его из шкафа и вдохнула в него новую жизнь. Оказывается, для оптимизации высоконагруженных виртуализованных платформ в контексте Zero-Copy, только RDMA и не хватало.

Принцип работы

Большинство устройств ПК нуждаются в периодическом обмене данными не только с центральным процессором (ЦП), но и с оперативной памятью. В первых вариантах персональных компьютеров процесс обмена данными какого-либо устройства с ОЗУ протекал при помощи процессора. Такой метод получил название PIO (Programmable Input-Output, программируемый ввод-вывод). Однако этот метод имел ряд недостатков. Прежде всего, было очевидно, что поскольку процессор загружен множеством задач, то он не всегда может отвлекаться на то, чтобы управлять процессом чтения и записи данных ОЗУ, тем более, что объем этих данных в результате прогресса компьютерной техники все увеличивался и увеличивался.

Так появилась идея технологии DMA (сокращение от Direct Memory Access, т.е. Прямой Доступ к Памяти), состоящая в том, чтобы позволить различным устройствам обращаться к оперативной памяти напрямую, минуя ЦП. Также часто используется русская аббревиатура данной технологии – ПДП.

Первоначально практическая реализация этой технологии (в материнских платах на основе шины ISA) была осуществлена при помощи встроенного в материнскую плату контроллера ПДП, который был призван управлять процессом обмена данными между устройством и ОЗУ. При этом процессор также не был полностью исключен из этого процесса. Прежде всего, механизм ПДП инициализировался самим процессором, однако в ход процесса передачи данных он не вмешивался, занимаясь в это время другими задачами. После того, как обмен информацией между устройством и ОЗУ завершался, то процессор получал соответствующее прерывание, которое отсылал ему контроллера DMA.

В шине ISA также использовались специальные каналы ПДП, которые часто закреплялись за отдельным устройством:

- Обновление DRAM

- Аппаратный пользовательский канал, обычно использовался для 8-битных звуковых карт

- Контроллер дисковода гибких дисков

- Жесткий диск. Канал не использовался для жестких дисков с поддержкой PIO, а затем с UDMA. Также канал использовался для некоторых звуковых карт и параллельного порта

- Каскадное прерывание от XT-контроллера ПДП

- Пользовательский канал, иногда использовался для жестких дисков или 16-битных звуковых карт

- Пользовательский канал

- Пользовательский канал

Обычно данные каналы можно было устанавливать программным путем, но на некоторых старых устройствах, например, картах расширения для подключения накопителей CD-ROM, необходимо было вручную устанавливать значения нужных каналов при помощи перемычек.

L-502

АЦП: 16 бит; 16/32 каналов;

±0,2 В…10 В; 2 МГц

ЦАП: 16 бит; 2 канала; ±5 В; 1 МГц

Цифровые входы/выходы:

17/16, ТТЛ 5 В

Интерфейс: USB 2.0 (high-speed), Ethernet (100 Мбит)

Гальваническая развязка.

Модуль АЦП/ЦАП

16/32 каналов, 16 бит, 2 МГц, USB, Ethernet

Совместимость системы

Защита DMA ядра требует новой поддержки прошивки UEFI. Ожидается, что эта поддержка будет поддерживаться только в недавно внедренных системах на основе Intel с Windows 10 версии 1803 (не во всех системах). Безопасность на основе виртуализации (VBS) не требуется.

Чтобы узнать, поддерживает ли система защиту от DMA ядра, Сведения о системе настольное приложение (MSINFO32). Системы, выпущенные до Windows 10 версии 1803, не поддерживают защиту DMA ядра, но могут использовать другие меры по смягчению последствий атак DMA, как описано в контрмерах BitLocker.

Защита DMA ядра не совместима с другими контрмерами атак DMA BitLocker. Рекомендуется отключить контрмеры атак DMA BitLocker, если система поддерживает защиту DMA ядра. Защита DMA ядра обеспечивает более высокую планку безопасности для системы в ответ на контрмеры атак DMA BitLocker, сохраняя при этом возможность использования внешних периферийных устройств.

Все ответы

- 17 марта 2010 г. 5:51 Ответить | Цитировать

- что-то я не понял… а это тогда что такое?http://img34.imageshack.us/img34/7185/sata.pngЕсли AHCI не используется, то SATA-диски эмулируются как IDE-устройства.17 марта 2010 г. 6:37 Ответить | Цитировать

- 17 марта 2010 г. 6:39 Ответить | Цитировать

- У меня материнская плата ASUS M2R32-MVP переключение дисков в AHCI приводит просто к темному экрану при попытке загрузить ОС. Переключение в RAID приводит к синиму экрану. Качал драйвера на чипсет, менял значения в реестре винда отказывается видить жесткие диски на SATA. Запускал востановление системы, давал ей драйвера, но ОС все равно не хочет увидеть еще 3 винта и СД.21 марта 2010 г. 21:32 Ответить | Цитировать

- Вот этими рекомендациями пробовали воспользоваться?MCSA21 марта 2010 г. 23:36 Ответить | Цитировать

- Да, так и стоит в реестре 023 марта 2010 г. 4:28 Ответить | Цитировать

Странно. У меня прокатило.Тогда остаётся одно — запуск установки Windows 7 в режиме восстановления Windows. Все проги и документы в этом случае останутся рабочими и процесс установки пройдёт гораздо быстрее. Хотя, документы по старой привычке я бы всё-таки куда-нибудь забэкапил.

MCSA23 марта 2010 г. 6:47 Ответить | Цитировать

Парни, все гораздо проще.

Вы не хотите использовать поиск.

23 марта 2010 г. 10:06 Ответить | Цитировать

В поиске пробыл я часа четыре, и перепробовал все, что смог найти, кроме переустановки Win 7. Перевести работу дисков на AHCI у меня так и не вышло, но заменив один из контроллеров IDE на стандартный контроллер ACHI все SATA винты и DVD раскидались по устройству на канал и DVD стал в DMA работать, так что проблема была решена. Если попытаться обновить стандартный контроллер ACHI на тот что на диске от материнской платы то все тот же синий экран в режиме RAID или темный экран в режиме ACHI , или длительная загрузка в режиме native , конца которой я спустя 10 мин так и не дождался…

Самопроизвольное переключение Виндовс на режим PIO и признаки этого

Windows по умолчанию работает с HDD в скоростном режиме DMA, но иногда из-за специфических ошибок самостоятельно переключается в режим PIO. Причем обратно включить DMA весьма проблематично и сделать это стандартными способами практически невозможно. Характерные признаки того, что Windows переключилась на работу с жестким диском в режим PIO это:

• Падение быстроты работы с HDD в несколько раз;

• Медленная скорость работы системы во время дисковых операций;

• Чрезмерная загрузка процессора (80-90%) при работе с жестким диском;

• Система начала «тормозить» резко. То есть еще час назад все было нормально, а потом резко появились проблемы.

На данный момент жесткий диск — это самое слабое место всей системы и падение его скорости работы даже в два раза приводит к катастрофическим последствиям. Для того чтобы убедиться, что Windows действительно переключилась на работу с жестким диском в медленный режим PIO нужно сделать следующее:

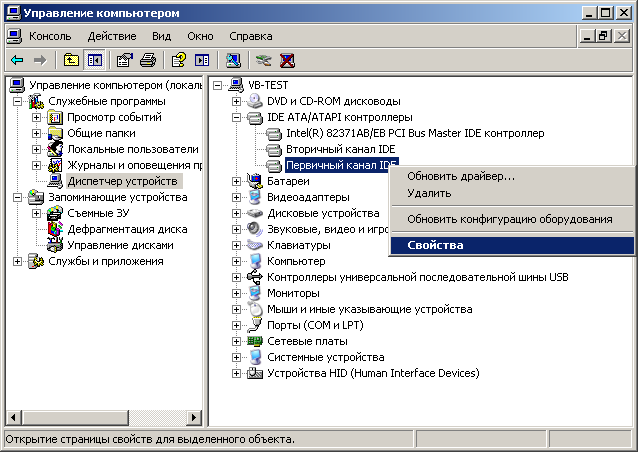

1. Нажмите на значок «Мой компьютер» правой клавишей мыши и выберите пункт «Управление»;

2. Раскройте ветку контроллера и найдите канал, к которому подключен ваш жесткий диск;

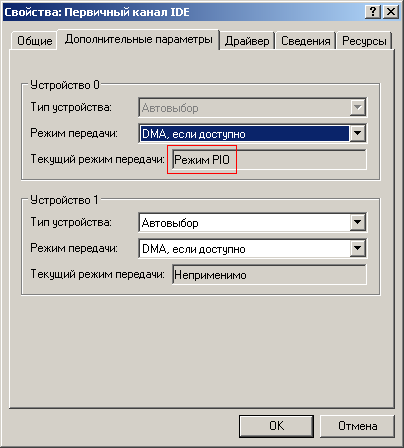

3. Нажмите на нем правую клавишу мыши, зайдите в «Свойства» и переключитесь на «Дополнительные параметры»;

4. Посмотрите на строку «Текущий режим передачи». Если там написано «Режим DMA», то значит все нормально, а вот если «Режим PIO», то вам придется проделать несколько несложных операций и вернуть диск в предпочтительный режим работы.

Регистры DMA

Доступ к регистрам можно выполнять как к байтам (8 бит), полусловам (16 бит) или словам (32 бита).

В используемых обозначениях под DMA подразумевается либо DMA1, либо DMA2, в зависимости от того, к регистру какого контроллера DMA мы хотим обратиться. В микроконтроллерах STM32F100xx семейств Low и Medium density Value Line имеется только DMA1 и всюду под DMA подразумевается DMA1.

Каждый канал DMA имеет либо свой регистр, либо своё битовое поле в общем регистре. Для обозначения номера канала будет использоваться символ «x», x=1..7 в случае DMA1 и x=1..5 для контроллера DMA2.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Reserved | TEIF7 | HTIF7 | TCIF7 | GIF7 | TEIF6 | HTIF6 | TCIF6 | GIF6 | TEIF5 | HTIF5 | TCIF5 | GIF5 | |||

| r | r | r | r | r | r | r | r | r | r | r | r | ||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TEIF4 | HTIF4 | TCIF4 | GIF4 | TEIF3 | HTIF3 | TCIF3 | GIF3 | TEIF2 | HTIF2 | TCIF2 | GIF2 | TEIF1 | HTIF1 | TCIF1 | GIF1 |

| r | r | r | r | r | r | r | r | r | r | r | r | r | r | r | r |

Address offset: 0x00

Reset value: 0x0000 0000

Регистр состояния прерывания, содержит набор флагов (по 4 флага на канал DMA), которые устанавливаются аппаратно при наступлении соответствующего события. Установка любого из флагов может привести к генерации прерывания, если это разрешено. Сброс флагов осуществляется с помощью регистра DMA_IFCR (сброс необходим при обработке прерываний от DMA).

TEIFx: Channel x transfer error flag

Флаг ошибки передачи в канале x, этот бит устанавливается аппаратно. Сбрасывается записью 1 в соответствующий бит регистра DMA_IFCR.

0: Не было ошибок передачи в DMA канале x.

1: На канале x произошла ошибка при пересылке данных.

HTIFx: Channel x half transfer flag

Флаг завершения передачи половины данных в канале x, бит устанавливается аппаратно. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

0: Не было события — завершения передачи половины от общего количества данных.

1: Было зафиксировано событие — завершение передачи половины данных.

TCIFx: Channel x transfer complete flag

Флаг завершения передачи в канале x, бит устанавливается аппаратно. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

0: Не было зафиксировано события — завершения передачи данных.

1: Было зафиксировано событие — завершение передачи данных.

GIFx: Channel x global interrupt flag

Глобальный флаг прерывания в канале x, бит устанавливается аппаратно одновременно с установкой любого из флагов для данного канала: TEIFx, HTIFx или TCIFx. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

0: Не происходило установки ни одного из флагов TEIFx, HTIFx или TCIFx на данном канале DMA.

1: Произошла установка одного из флагов TEIFx, HTIFx или TCIFx.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Reserved | CTEIF7 | CHTIF7 | CTCIF7 | CGIF7 | CTEIF6 | CHTIF6 | CTCIF6 | CGIF6 | CTEIF5 | CHTIF5 | CTCIF5 | CGIF5 | |||

| w | w | w | w | w | w | w | w | w | w | w | w | ||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CTEIF4 | CHTIF4 | CTCIF4 | CGIF4 | CTEIF3 | CHTIF3 | CTCIF3 | CGIF3 | CTEIF2 | CHTIF2 | CTCIF2 | CGIF2 | CTEIF1 | CHTIF1 | CTCIF1 | CGIF1 |

| w | w | w | w | w | w | w | w | w | w | w | w | w | w | w | w |

Address offset: 0x04

Reset value: 0x0000 0000

Регистр сброса флагов прерывания. Биты данного регистра используются для программного сброса соответствующих битов в регистре флагов DMA_ISR путём записи в бит значения 1, запись в бит 0 не имеет никакого эффекта.

CTEIFx: Channel x transfer error clear

Сброс флага ошибки передачи в канале x.

0: Не имеет эффекта.

1: Сброс флага TEIFx в регистре DMA_ISR.

CHTIFx: Channel x half transfer clear

Сброс флага половинной передачи в канале x.

0: Не имеет эффекта.

1: Сброс флага HTIFx в регистре DMA_ISR.

CTCIFx: Channel x transfer complete clear

Сброс флага завершения передачи в канале x.

0: Не имеет эффекта.

1: Сброс флага TCIFx в регистре DMA_ISR.

CGIFx: Channel x global interrupt clear

Сброс флагов в канале x.

0: Не имеет эффекта.

1: Сброс всех флагов для канала x в регистре DMA_ISR (GIFx, TEIFx, HTIFx и TCIFx).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Reserved | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Res. | MEM2 MEM |

PL[1:0] | MSIZE[1:0] | PSIZE[1:0] | MINC | PINC | CIRC | DIR | TEIE | HTIE | TCIE | EN | |||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | |

Address offset: 0x08+0d20*(x–1)

Reset value: 0x0000 0000

Конфигурационный регистр. Каждый канал имеет свой выделенный конфигурационный регистр, который используется для настройки и включения этого канала DMA.

MEM2MEM: Memory to memory mode

Включение режима «memory to memory» (копирование данных из памяти в память). Бит устанавливается и сбрасывается программно.

0: Режим «memory to memory» отключён.

1: Режим включён.

PL[1:0]: Channel priority level

Уровень приоритета канала. Битовое поле задаётся программно и определяет уровень приоритета канала в соответствии со значениями:

00: низкий;

01: средний;

10: высокий;

11: очень высокий.

MSIZE[1:0]: Memory size

Размер элемента данных в памяти. Битовое поле задаётся программно и определяет размер одного элемента данных, записываемого в память или считываемого из памяти (зависит от выбранного направления передачи) за одну транзакцию:

00: 8 бит (передача по байтам);

01: 16 бит (передача по полусловам);

10: 32 бита (передача по словам);

11: зарезервировано (не используется).

PSIZE[1:0]: Peripheral size

Размер элемента данных для обмена с периферийным устройством. Битовое поле задаётся программно и определяет размер одного элемента данных, считываемого из регистра периферийного устройства или записываемого в него (в зависимости от выбранного направления передачи) за одну транзакцию:

00: 8 бит (передача по байтам);

01: 16 бит (передача по полусловам);

10: 32 бита (передача по словам);

11: зарезервировано (не используется).

MINC: Memory increment mode

Режим инкрементирования адреса в памяти. Этот бит устанавливается и сбрасывается программно.

0: Инкрементирование адреса отключено.

1: Инкрементирование адреса включено.

PINC: Peripheral increment mode

Режим инкрементирования адреса периферии. Бит устанавливается и сбрасывается программно.

0: Инкрементирование адреса отключено.

1: Инкрементирование адреса включено.

CIRC: Circular mode

Циклический режим. Бит устанавливается и сбрасывается программно.

0: Циклический режим отключён.

1: Циклический режим включён.

DIR: Data transfer direction

Направление передачи данных. Бит устанавливается и сбрасывается программно.

0: Чтение данных из периферийного устройства.

1: Чтение данных из памяти.

TEIE: Transfer error interrupt enable

Разрешение прерываний при возникновении ошибок передачи. Этот бит устанавливается и сбрасывается программно.

0: Генерация прерываний при возникновении ошибок передачи отключена.

1: Генерация прерываний при возникновении ошибок передачи включена.

HTIE: Half transfer interrupt enable

Разрешение прерываний при завершении передачи половины данных. Бит устанавливается и сбрасывается программно.

0: Генерация прерываний при завершении передачи половины данных отключена.

1: Генерация прерываний при завершении передачи половины данных включена.

TCIE: Transfer complete interrupt enable

Разрешение прерываний при завершении передачи данных. Бит устанавливается и сбрасывается программно.

0: Генерация прерываний при завершении передачи данных отключена.

1: Генерация прерываний при завершении передачи данных включена.

EN: Channel enable

Включение канала. Бит устанавливается и сбрасывается программно.

0: Канал отключён.

1: Канал включён.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| Reserved | |||||||||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| NDT | |||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Address offset: 0x0C+0d20*(x–1)

Reset value: 0x0000 0000

NDT[15:0]: Number of data to transfer

Количество элементов для передачи (общее количество транзакций), от 0 до 65535. В этот регистр можно записывать только при отключённом канале. После включения канала, регистр становится доступным только для чтения и содержит оставшееся количество элементов для передачи (или количество транзакций). Это количество в общем случае не равно объёму данных в байтах, т.к. размер одного элемента может быть более одного байта (может быть равным 2 или 4 байтам).

Содержимое регистра уменьшается на 1 после каждой DMA передачи (после каждой транзакции). Когда значение регистра достигает 0, передача останавливается (в нециклическом режиме) или регистр автоматически перезагружается первоначально записанным в него значением и передача продолжается (в циклическом режиме).

Если в регистр записано значение 0, транзакции не выполняются, независимо от того, включен DMA канал или нет.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| PA | |||||||||||||||||||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Address offset: 0x10+0d20*(x–1)

Reset value: 0x0000 0000

Не допускается запись в регистр при включённом данном канале DMA.

PA[31:0]: Peripheral address

Базовый адрес регистра периферийного устройства из которого выполняется чтение или в который производится запись. Если размер данных периферийного устройства установлен равным 16 бит (PSIZE: 01), доступ осуществляется с автоматическим выравниванием на полуслово (младший бит PA[0] игнорируется). Если размер данных периферийного устройства установлен равным 32 бита (PSIZE: 10), доступ осуществляется с автоматическим выравниванием на слово (два младших бита PA[1:0] игнорируются).

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MA | |||||||||||||||||||||||||||||||

| rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

Address offset: 0x14+0d20*(x–1)

Reset value: 0x0000 0000

Не допускается запись в регистр при включённом данном канале DMA.

MA[31:0]: Memory address

Базовый адрес памяти, по которому выполняется запись или чтение. Если размер данных в памяти установлен равным 16 бит (MSIZE: 01), доступ осуществляется с автоматическим выравниванием на полуслово (младший бит MA[0] игнорируется). Если размер данных в памяти установлен равным 32 бита (MSIZE: 10), доступ осуществляется с автоматическим выравниванием на слово (два младших бита MA[1:0] игнорируются).