Арифметико-логическое устройство

Арифметико-логическое устройство (АЛУ) — центральная часть процессора, выполняющая арифметические и логические операции.

АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ подразделяются на три основные категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление. ). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ. ). Операции над битами обычно подразумевают сдвиги.

Определение понятия

Арифметико-логическое устройство — один из блоков процессора, управляемый УУ (устройством управления). Его предназначение: выполнение логических и арифметических преобразований над данными-операндами (аргументами операции, информацией, обрабатываемой программой). Разрядность операндов в данном случае — размер или длина машинного слова.

Современное многофункциональное АЛУ состоит сегодня из двух частей:

- Операционное устройство.

- Устройство управления. Проводит вторичную дешифрацию кодов команды, определяет операцию, выполняемую в арифметико-логическом устройстве.

Классификация АЛУ

Мы помним, арифметико-логическое устройство — устройство управления и операционное. Но не все современные и исторические АЛУ одинаковы. Далее мы приведем самые распространенные их классификации.

По способу представления информации:

- С плавающей запятой.

- С фиксированной запятой.

По способу действий с операндами:

- Параллельные. В этом случае операции над всеми разрядами выполняются АЛУ одновременно.

- Последовательные. В данном случае операции будут выполняться по очереди, последовательно над каждым из разрядов.

- Параллельно-последовательные. Слово данных здесь делится на слоги. Обработка информации в таком АЛУ (арифметико-логическом устройстве) ведется параллельно над разрядами слога и последовательно над самими слогами.

По применению систем исчисления:

- Двоичные.

- Двоично-десятичные.

- Восьмеричные.

- Шестнадцатиричные и проч.

По особенностям использования узлов и элементов:

- Блочные. Для выполнения отдельных арифметических операций в систему арифметико-логического устройства процессора вводят специальные блоки. Последние позволяют вести параллельно процессы обработки информации.

- Конвейерные. Чем отличаются АЛУ такого типа? Любая операция будет разбиваться на последовательность из микроопераций. Они выполняются за определенные такты (равные временные промежутки) на разных ступенях такого конвейера. Операция над потоком операндов, таким образом, выполняется каждый такт.

- Многофункциональные. Это универсальные АЛУ, которые способны исполнить множество операций в одном устройстве. Однако здесь требуется настройка на выполнение конкретной операции с помощью ее кода.

Вам будет интересно: GeForce GT 720M: обзор, характеристики и отзывы

По временным характеристикам:

- Синхронные. В таких арифметико-логических устройствах компьютера каждая операция станет выполняться за один такт.

- Асинхронные. Соответственно, нетактируемые АЛУ. Обеспечивают высокую степень быстродействия, так как выполняются на комбинационных схемах.

По характеристике устройства управления:

- Имеющие микропрограммное управление.

- С жесткой логикой УУ.

Действие устройства управления процессора

Этот блок отвечает за выработку последовательности функциональных сигналов, нужной для корректного выполнения заданной команды. Как правило, такие преобразования реализуются за несколько тактов.

Управляющее устройство обеспечивает автоматическое выполнение программы. При этом задействуются необходимые координированные ответвления работы прочих составляющих компонентов машины.

За действие устройства управления отвечает базовый принцип микропрограммирования, имеющий четкое число характеристик.

Операция округления в АЛУ

С помощью опции RND аккумулятор позволяет округлять 40–битный результат до 16–битного. Округленный результат передается в регистр MR или MF. При использовании регистра MR округленный 16–битный результат содержится в регистре MR1. Содержимое регистров MR2, MR1 можно рассматривать как результат, округленный до 24 бит. Устройство сдвига.

Устройство сдвига SHIFTER предназначено для выполнения сдвиговых операций 16–разрядных операндов, включающих арифметические и логические сдвиги, нормализацию и денормализацию, определение экспоненты. Устройство сдвига содержит (рис. 8.3.5):

- сдвиговый массив размерности 16×32, в котором исходный 16–разрядный операнд за один цикл помещается на любую позицию в 32–разрядном выходном слове, начиная с полностью сдвинутого операнда вправо и кончая полностью сдвинутым операндом влево;

- детектор экспоненты дляопределения степени операнда (см. ниже);

- регистр операндов SI (Shifter InOut), обеспечивающий 16–разрядный операнд для сдвигового массива и детектора экспоненты;

- регистр результата SR (Shifter Result) для хранения 32–разрядного результата сдвигового массива, состоящий из двух 16–битных регистров SR0, SR1. Информация в регистр SR может быть занесена с шины данных памяти данных DMD и считана на шины DMD и R. Регистр SR может быть также задействован в цепи обратной связи через логику управления OR/PASS для реализации сдвигов с двойной точностью;

- восьмиразрядный регистр экспоненты SE (Shifter Exponent), содержащий порядок в виде 8–разрядного дополнительного кода при выполнении операций нормализации и денормализации;

- пятиразрядный регистр для блочных операций с плавающей точкой SB (Shifter Block). Он содержит значение экспоненты блока, т. е. то значение, на которое компоненты блока должны быть сдвинуты, чтобы нормализовать самое большое значение. Чтение и запись регистра осуществляется через 5 младших разрядов шины DMD. Значения записываются в дополнительном коде в формате 5.0;

- логику OR/PASS, позволяющую получить правильный результат (см. приведенные ниже примеры) при операциях с двойной точностью. При выборе модификатора PASS результат сдвигового массива загружается в регистр SR без изменения. С помощью модификатора OR выполняется операция ИЛИ над результатом сдвигового массива и текущим содержимым регистра SR. Результат операции ИЛИ помещается в регистр SR. При считывании информации из регистров SE, SB на шину DMD происходит расширение знака до 16–битного значения. Устройство сдвига содержит два банка регистров SI, SE, SR, SB. Для выбора банка используется бит SEC_REG в позиции MSTAT.0 регистра режима и статуса MSTAT (табл. 8.3.9).

Содержание

Разработчик компьютера ENIAC, Джон фон Нейман, был первым создателем АЛУ. В 1945 году он опубликовал первые научные работы по новому компьютеру, названному EDVAC (Electronic Discrete Variable Computer). Годом позже он работал со своими коллегами над разработкой компьютера для Принстонского института новейших исследований (IAS). Архитектура этого компьютера позже стала прототипом архитектур большинства последующих компьютеров. В своих работах фон Нейман указывал устройства, которые, как он считал, должны присутствовать в компьютерах. Среди этих устройств присутствовало и АЛУ. Фон Нейман отмечал, что АЛУ необходимо для компьютера, поскольку оно гарантирует, что компьютер будет способен выполнять базовые математические операции включая сложение, вычитание, умножение и деление

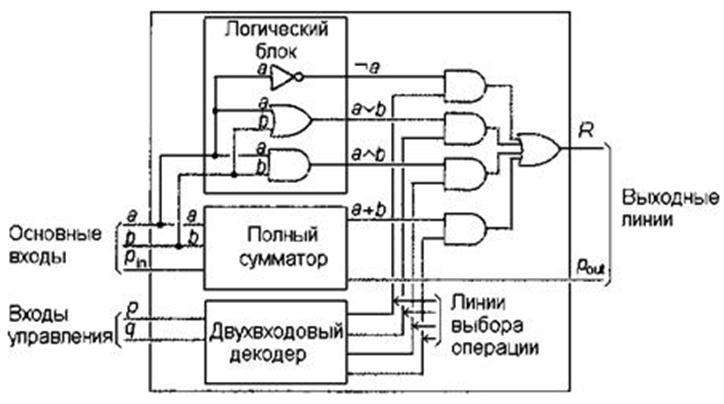

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и элемента управления выполняемым процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части :

- микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

- операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

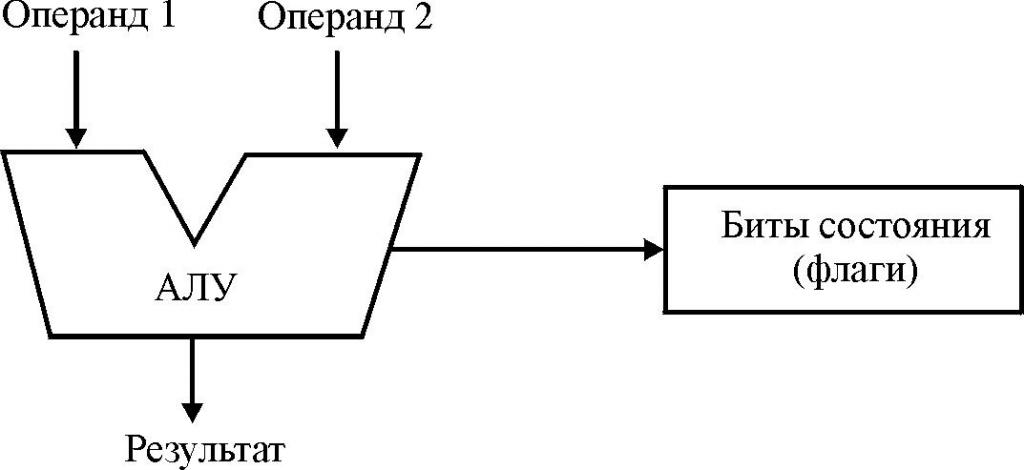

Рисунок 1 — Структурная схема арифметико-логического устройства

Структурная схема АЛУ и его связь с другими блоками машины показаны на рисунке 1. В состав АЛУ входят регистры Рг1 — Рг7, в которых обрабатывается информация , поступающая из оперативной или пассивной памяти N1, N2, . NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Закон переработки информации задает микропрограмма , которая записывается в виде последовательности микрокоманд A1,A2, . Аn-1,An. При этом различают два вида микрокоманд: внешние, то есть такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 1 микрокоманды A1,A2. Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд. Например, АЛУ может генерировать признаки в зависимости от результата вычислений: признак переполнения, признак отрицательного числа, признак равенства 0 всех разрядов числа др. На рис. 1 эти микрокоманды обозначены р1, p2. рm.

Результаты вычислений из АЛУ передаются по кодовым шинам записи у1, у2, . уs, в ОЗУ. Функции регистров, входящих в АЛУ:

- Рг1 — сумматор (или сумматоры) — основной регистр АЛУ, в котором образуется результат вычислений;

- Рг2, РгЗ — регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции);

- Рг4 — адресный регистр (или адресные регистры), предназначен для запоминания (иногда и формирования) адреса операндов и результата;

- Ргб — k индексных регистров, содержимое которых используется для формирования адресов;

- Рг7 — i вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров является программно-доступной, то есть они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся : сумматор, индексные регистры, некоторые вспомогательные регистры.

Остальные регистры программно-недоступные, так как они не могут быть адресованы в программе. Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу обработки информации и логической структуре.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования «операция/ режим адресации» базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

Статьи к прочтению:

Основной элементарной операцией, выполняемой над кодами чисел в цифровых устройствах, является арифметическое сложение. Сумматор – электронная логическая…

Файлы операционной системы хранятся во внешней, долговременной памяти (на жестком, гибком или лазерном диске). Однако программы могут выполняться, только…

Операции в устройстве

И еще одна тема напоследок. Мы должны помнить, что все операции,выполняемые в АЛУ, — логические. Их можно разделить на следующие категории:

- Индексной арифметики.

- Десятичной арифметики.

- Специальной арифметики.

- Двоичной арифметики для значений с фиксированной точкой.

- Двоичной, шестнадцатеричной арифметики для значений с плавающей точкой.

- Над алфавитно-цифровыми полями.

- Над логическими кодами.

Арифметико-логическое устройство — основная часть процессора любого компьютера. Было разработано еще в середине прошлого века прославленным фон Нейманом. Призвано исполнять простые арифметические и логические операции в компьютере. Сегодня существует большое количество разновидностей АЛУ, что видно из множества представленных классификаций данных устройств.