Принцип открытой архитектуры компьютера и современные тенденции развития

Компьютерная архитектура (computer architecture) – это разработанный Джоном фон Нейманом набор правил и методов описания функций, которые участвуют в организации работы компьютерных систем. Впервые документальное упоминание данного термина найдено в переписке английского ученого Чарльза Бэббиджа с писательницей и математиком Адой Лавлейс в первой половине ХХ века.

Понятие архитектуры персонального компьютера (ПК) дает нам представление о том, как он устроен, как разные устройства взаимодействуют друг с другом. Они подсоединяются по определенной схеме, а ее вариации и будут разновидностями архитектурных систем.

Любой современный персональный компьютер или ноутбук – это сложное многофункциональное устройство, а не просто мультиплатформенная игровая приставка. Всего можно выделить пять уровней архитектуры электронно вычислительных машин (ЭВМ):

- нулевой уровень;

- первый уровень – микроархитектура компьютера;

- второй – системные команды;

- третий – операционная система;

- четвертый – прикладные и системные программы;

- пятый – уровень высокого языка.

Цифровой логический уровень

Цифровой логический уровень по сути представляет собой набор логических функций, которые взаимодействую между собой для выполнения большей задачи. Вся работа этого уровня заключается в двух базовых концепциях: вентили и булева алгебра. Сначала я расскажу про них, а дальше про логические схемы и то как они используются при разработке, и в заключении, то что из себя представляет память и как она реализуется.

Вентиль (рис. 1.0) является устройством, которое принимает входные сигналы и выдает выходные, сам он реализован на транзисторах (об их работе я рассказывать не буду). Вентили используются на данном уровне как «строительный» материал, чтобы представлять базовые логические операции, а дальше уже идет их комбинирование для реализации тех или иных схем, то есть смысл данного уровня заключается в построении переиспользуемых схем, а не о работе вентилей (и транзисторов); дальше уже на основе этих схем могут быть построены более сложные и узкоспециализированные схемы, например, целые модули памяти, различная логика, например, для того как будут взаимодействовать компоненты CPU на уровне микроархитектуры и тд.

Рисунок 1.0. Изображение вентилей.

Таблица 1.0. Таблица истинности для основных операций.

| A | B | И | И-НЕ | ИЛИ | ИЛИ-НЕ | ИСК-ИЛИ |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 |

Современные многоуровневые компьютеры

Современные компьютеры можно представить как структуру, состоящую из 6 уровней:

Структура шестиуровневого компьютера

Ради полноты нужно упомянуть о существовании еще одного уровня, который расположен ниже нулевого. Этот уровень не показан на рис. выше, так как он попадает в сферу электронной техники и, следовательно, не рассматривается из-за сложности материала. Он называется уровнем физических устройств. На этом уровне находятся транзисторы, которые для разработчиков компьютеров являются примитивами. Объяснить, как работают транзисторы, — задача физики.

Уровень 0: Цифровой логический уровень

Объекты цифрового логического уровня — вентили. Хотя вентили состоят из аналоговых компонентов, таких как транзисторы, они могут быть точно смоделированы как цифровые устройства. У каждого вентиля есть один или несколько цифровых входов (сигналов, представляющих 0 или 1). Вентиль вычисляет простые функции этих сигналов, такие как И или ИЛИ. Каждый вентиль формируется из нескольких транзисторов. Несколько вентилей формируют 1 бит памяти, который может содержать 0 или 1. Биты памяти, объединенные в группы, например, по 16, 32 или 64, формируют регистры. Каждый регистр может содержать одно двоичное число до определенного предела. Из вентилей также может состоять сам компьютер.

Уровень 1: уровень Микроархитектуры

Следующий уровень называется уровнем микроархитектуры. На этом уровне находятся совокупности 8 или 32 регистров, которые формируют локальную память и схему, называемую АЛУ (арифметико-логическое устройство). АЛУ выполняет простые арифметические операции. Регистры вместе с АЛУ формируют тракт данных, по которому поступают данные. Тракт данных работает следующим образом. Выбирается один или два регистра, АЛУ производит над ними какую-либо операцию, например сложения, после чего результат вновь помещается в один из этих регистров.

На некоторых машинах работа тракта данных контролируется особой программой, которая называется микропрограммой. На других машинах тракт данных контролируется аппаратными средствами.

На машинах, где тракт данных контролируется программным обеспечением, микропрограмма — это интерпретатор для команд на уровне 2. Микропрограмма вызывает команды из памяти и выполняет их одну за другой, используя при этом тракт данных. Например, при выполнении команды ADD она вызывается из памяти, ее операнды помещаются в регистры, АЛУ вычисляет сумму, а затем результат переправляется обратно. На компьютере с аппаратным контролем тракта данных происходит такая же процедура, но при этом нет программы, интерпретирующей команды уровня 2.

Уровень 2: уровень архитектуры набора команд

Уровень 2 мы будем называть уровнем архитектуры набора команд. Каждый производитель публикует руководство для компьютеров, которые он продает, под названием «Руководство по машинному языку X», «Принципы работы компьютера У» и т. п. Подобное руководство содержит информацию именно об этом уровне. Описываемый в нем набор машинных команд в действительности выполняется микропрограммой-интерпретатором или аппаратным обеспечением. Если производитель поставляет два интерпретатора для одной машины, он должен издать два руководства по машинному языку, отдельно для каждого интерпретатора.

Уровень 3: уровень операционной системы

Этот уровень обычно является гибридным. Большинство команд в его языке есть также и на уровне архитектуры набора команд (команды, имеющиеся на одном из уровней, вполне могут быть представлены и на других уровнях). У этого уровня есть некоторые дополнительные особенности: новый набор команд, другая организация памяти, способность выполнять две и более программы одновременно и некоторые другие. При построении уровня 3 возможно больше вариантов, чем при построении уровней 1 и 2.

Новые средства, появившиеся на уровне 3, выполняются интерпретатором, который работает на втором уровне. Этот интерпретатор был когда-то назван операционной системой. Команды уровня 3, идентичные командам уровня 2, выполняются микропрограммой или аппаратным обеспечением, но не операционной системой. Другими словами, одна часть команд уровня 3 интерпретируется операционной системой, а другая часть — микропрограммой. Вот почему этот уровень считается гибридным. Мы будем называть этот уровень уровнем операционной системы.

Между уровнями уровнем архитектуры набора команд и уровнем операционной системы есть существенная разница. Нижние три уровня задуманы не для того, чтобы с ними работал обычный программист. Они изначально ориентированы на интерпретаторы и трансляторы, поддерживающие более высокие уровни. Эти трансляторы и интерпретаторы составляются так называемыми системными программистами, которые специализируются на разработке новых виртуальных машин. Уровни с четвертого и выше предназначены для прикладных программистов, решающих конкретные задачи.

Еще одно изменение, появившееся на уровне операционной системы, — механизм поддержки более высоких уровней. Уровни 2 и 3 обычно интерпретируются, а уровни 4, 5 и выше

обычно, хотя и не всегда, транслируются.

Другое отличие между уровнями 1, 2, 3 и уровнями 4, 5 и выше — особенность языка. Машинные языки уровней 1, 2 и 3 — цифровые. Программы, написанные на этих языках, состоят из длинных рядов цифр, которые воспринимаются компьютерами, но малопонятны для людей. Начиная с уровня 4, языки содержат слова и сокращения, понятные человеку.

Уровень 4: уровень Ассемблера

Уровень 4 представляет собой символическую форму одного из языков более низкого уровня. На этом уровне можно писать программы в приемлемой для человека форме. Эти программы сначала транслируются на язык уровня 1, 2 или 3, а затем интерпретируются соответствующей виртуальной или фактически существующей машиной. Программа, которая выполняет трансляцию, называется ассемблером.

Уровень 5: уровень языка прикладных программистов

Уровень 5 обычно состоит из языков, разработанных для прикладных программистов. Такие языки называются языками высокого уровня. Существуют сотни языков высокого уровня. Наиболее известные среди них — С, C++, Java, LISP и Prolog. Программы, написанные на этих языках, обычно транслируются на уровень 3 или 4. Трансляторы, которые обрабатывают эти программы, называются компиляторами. Отметим, что иногда также имеет место интерпретация. Например, программы на языке Java сначала транслируются на язык, напоминающий ISA и называемый байт-кодом Java, который затем интерпретируется.

В некоторых случаях уровень 5 состоит из интерпретатора для конкретной прикладной области, например символической логики. Он предусматривает данные и операции для решения задач в этой области, выраженные при помощи специальной терминологии.

Таким образом, компьютер проектируется как иерархическая структура уровней, которые надстраиваются друг над другом. Каждый уровень представляет собой определенную абстракцию различных объектов и операций. Рассматривая компьютер подобным образом, мы можем не принимать во внимание ненужные нам детали и, таким образом, сделать сложный предмет более простым для понимания.

Набор типов данных, операций и характеристик каждого отдельно взятого уровня называется архитектурой. Архитектура связана с программными аспектами. Например, сведения о том, сколько памяти можно использовать при написании программы, — часть архитектуры. Аспекты реализации (например, технология, применяемая при реализации памяти) не являются частью архитектуры. Изучая методы проектирования программных элементов компьютерной системы, мы изучаем компьютерную архитектуру. На практике термины «компьютерная архитектура» и «компьютерная организация» употребляются как синонимы.

По материалам книги «Архитектура компьютера» Э. Таненбаума. Советую прочитать оригинал.

Логические схемы

Логическая схема — это набор объединенных вентилей с входными и выходными сигналами. На рис 1.1 то же изображена схема у которой входными сигналами являются A и B, выходной сигнал идет от операции ИЛИ; так же у нее есть три вентиля: два И, один ИЛИ. Теперь давайте рассмотрим некоторые виды схем с которыми нам потребуется встречаться в дальнейшем, к ним относится: комбинационные, арифметические, интегральные схемы.

Комбинационные схемы

Комбинационная схема — это схема с одним дополнительным свойством: значение выходных сигналов зависят только от входных, или другими словами, в ней нет никаких запоминающих устройств. Из этого вида схем создаются переиспользуемые компоненты, которые применяются для реализации большинства других схем, мы рассмотрим несколько, а именно: компаратор, декодер, мультиплексор/демультиплексор.

Компаратор

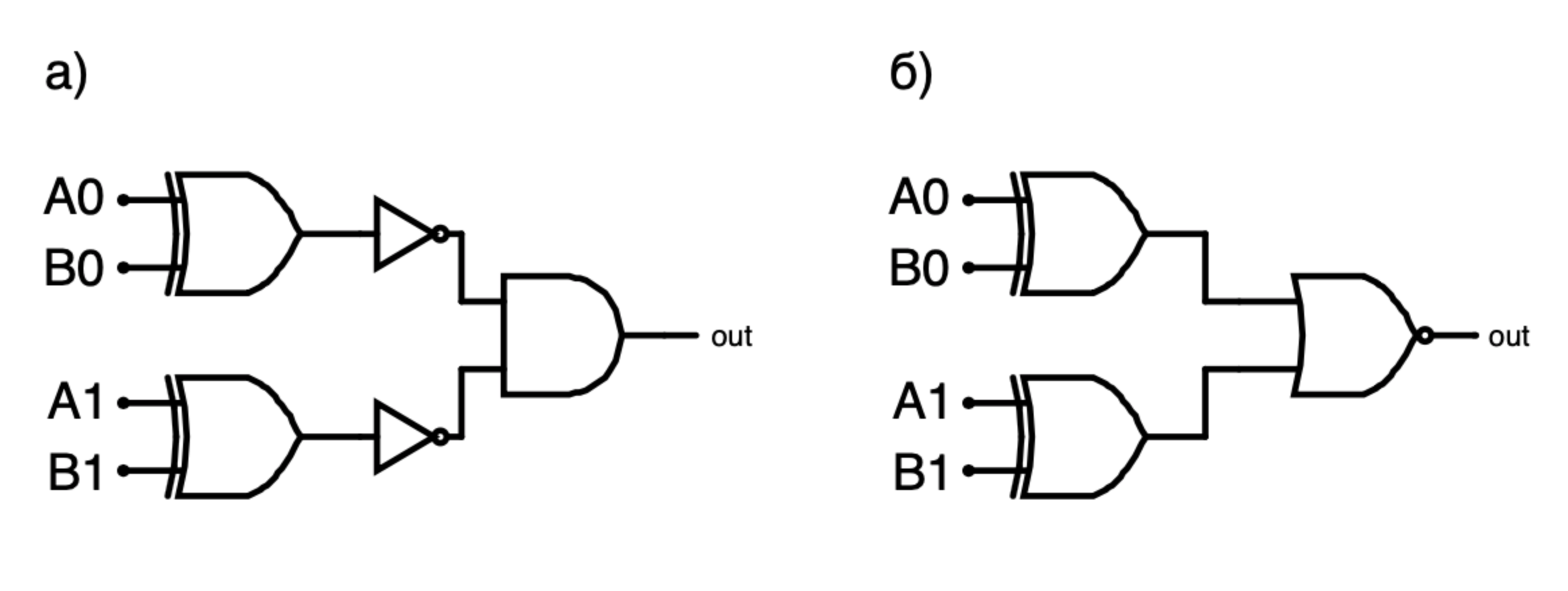

Компаратор имеет n входных парных линий (то есть 2n входов) и одну выходную линию. Логика его работы заключается в том, чтобы сравнить каждую пару битов (биты слова A сравниваются с соответствующими битами слова B) и при неравенстве хоть одной из них выдать 0 (если за ложь принят 0), иначе 1. Давайте построим таблицу истинности (табл. 1.1) для однобитного компаратора; можно заметить, что она равна таблице истинности ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ (когда к операции добавлен НЕ, то все выходные значение в таблице становятся противоположными). Теперь давайте расширим его до двухбитного компаратора, построим таблицу истинности (табл. 1.2) для него от двух переменных значения которых зависит от двух однобитных компаратора, то есть от двух ИСКЛЮЧАЮЩЕГО ИЛИ-НЕ; в ней значение 1 в CMP0 (и CMP1) значит, что два входа какото-то компаратора равны, 0 наоборот, то есть 1 в столбце R должна быть только, когда значения равны в двух компараторах. Эта таблица истинности совпадает с таблицей И, то есть мы объединяем все ИСКЛЮЧАЮЩЕГО ИЛИ-НЕ операцией И и у нас получится двухбитный компаратор (рис. 1.3а). Для дальнейшего расширение компаратора необходимо лишь добавить ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и подсоединить его к И. Недостаток такой реализации заключается в ее избыточности, нам требуется добавлять вентили НЕ для каждого ИСКЛЮЧАЮЩЕГО ИЛИ; мы можем от этого избавится (рис. 1.3б), если заменим вентиль И с НЕ входами на ИЛИ-НЕ, так как их таблицы истинности совпадают.

Таблица. 1.1. Таблица истинности для однобитного компаратора.

| A | B | CMP |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Таблица. 1.2. Таблица истинности для двухбитного компаратора.

| CMP0 | CMP1 | R |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Рисунок 1.3. Две схемы двухбитных компараторов.

Декодер

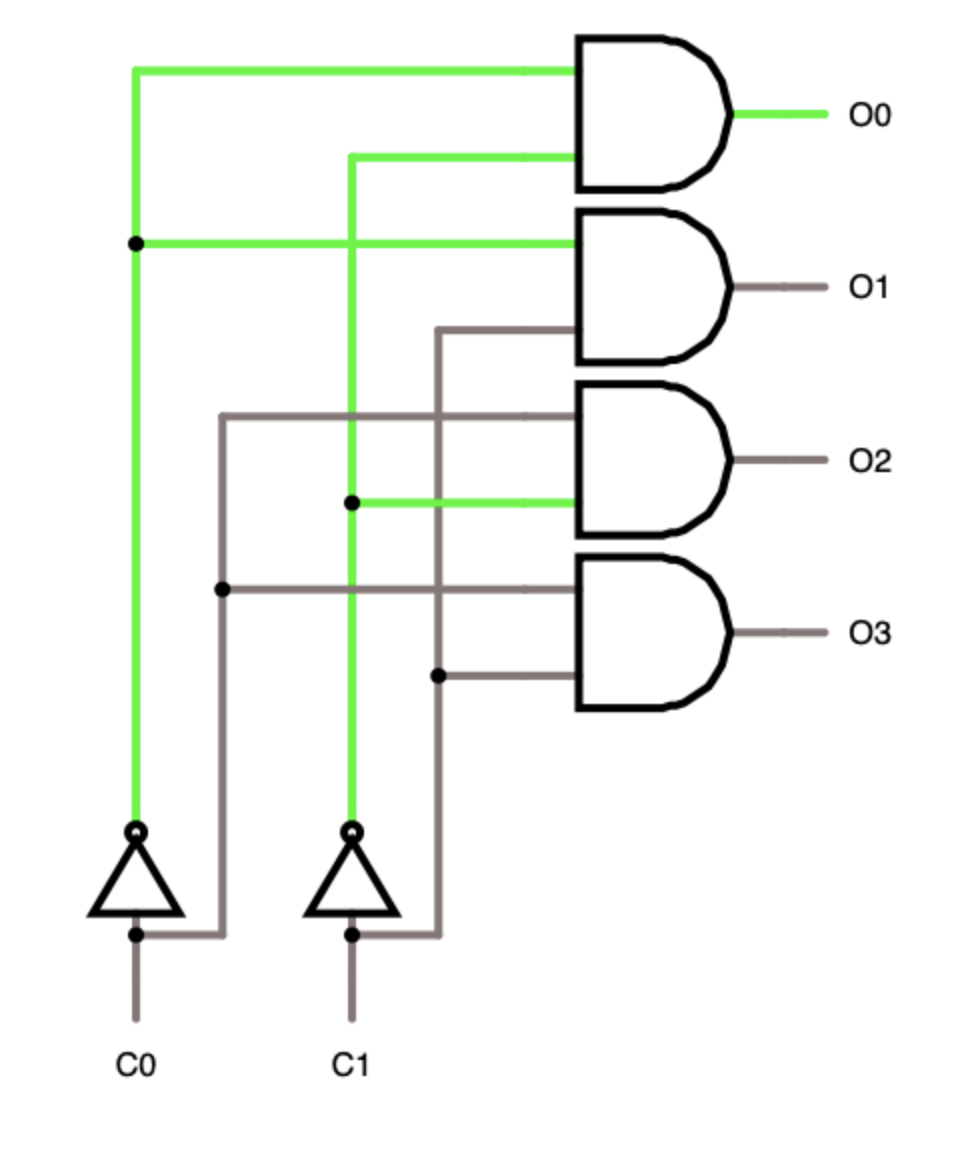

Декодер обладает n входными линиями, 2^n выходными, он реализован так, чтобы сигнал (истинна, 1) прошел только в одну выходную линию. Каждый выходной вентиль И получает свою комбинацию значений переменных, которые (значения) находятся в какой-то строке таблицы истинности, а как мы уже знаем, строку таблицы истинности можно реализовать как минтерму, то есть мы каждую строку представляем как вентиль И (рис. 1.4) от нескольких переменных. Основное применение декодера заключается в выборочном включении разных частей схемы (или схем), например, у АЛУ (о нем далее) имеется несколько операции, которые он может выполнять над входными значениями, чтобы их выбрать одну из них используется декодер.

Рисунок 1.4 Декодер.

Мультиплексор/демультиплексор

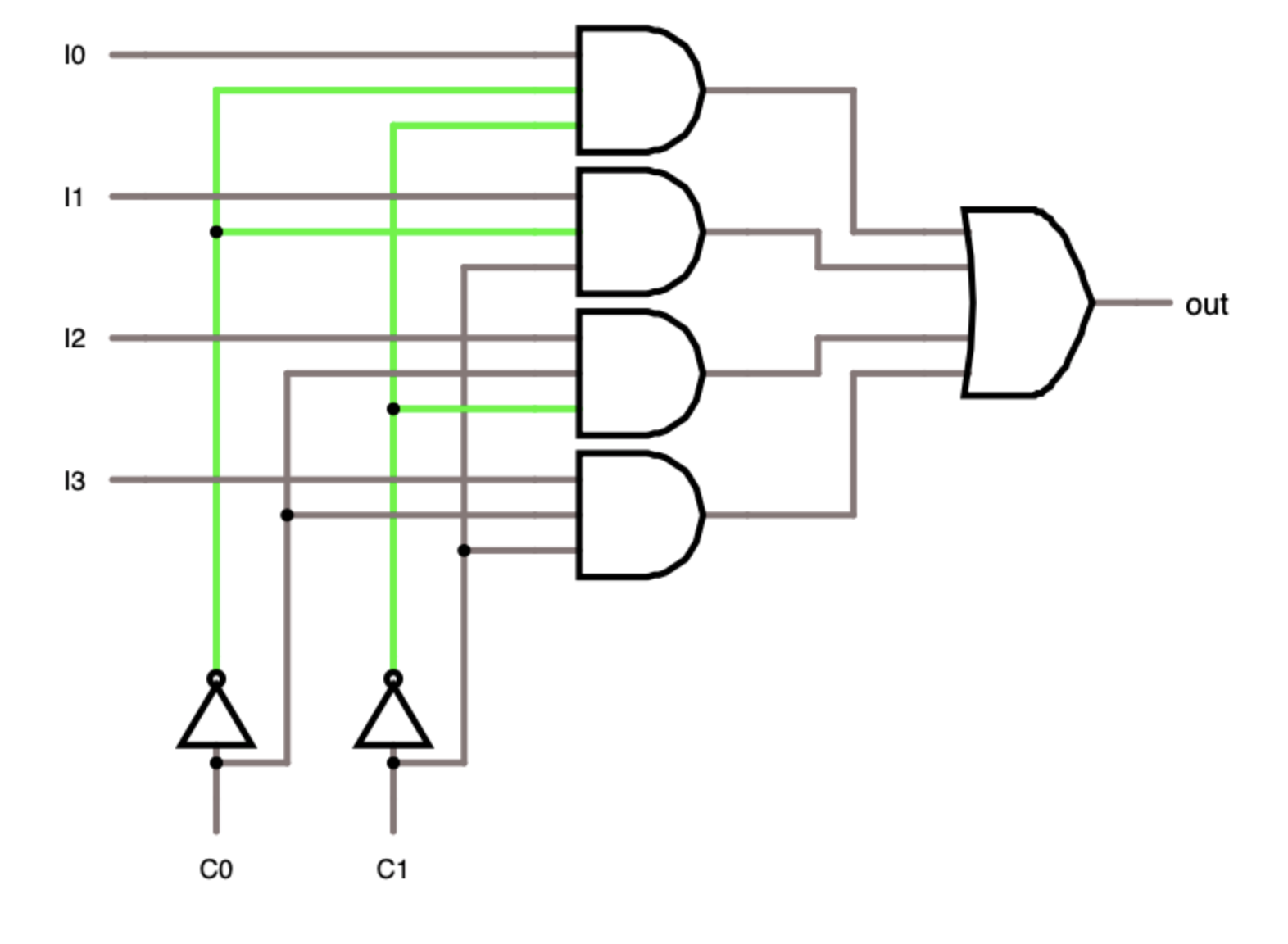

Мультиплексор обладает 2^n входными линиями, n линиями управление и одной выходной линией. Он в реализации в какой-то степени похож (рис 1.5) на декодер, если представить входы декодера как линии управления, дополнить каждый вентиль И дополнительным входным сигналом и объединить выходные значение всех И одним ИЛИ. Суть его работы заключается в том, чтобы на выход поступал сигнал только от одного из возможных входных линий. Мультиплексор применяется в разных целях, например, он может пригодиться для преобразования параллельного кода в последовательный. Допустим у нас есть параллельная (это значит, что линии работают одновременно) шина с несколькими линиями по которым параллельно передаются биты; чтобы считать нужное нам слово (обычно разрядность слова соответствует разрядности регистра в процессоре) мы соединяем линий шины с входами мультиплексора и последовательно включаем по одному входу, допустим сверху-вниз, тем самым на выход у нас пойдет точная последовательность битов.

Демультиплексор является обратным мультиплексору, он имеет одну входную линию, n линий управления и 2^n выходных линий. Логика его работу точно, такая же как и в мультиплексоре, только один входной сигнал идет в один из выходных. Может быть использован для преобразования последовательного кода в параллельный.

Рисунок 1.5. Мультиплексор.

Арифметические схема

Данный вид схем выполняет арифметические операции над входными сигналами. Основными схемами являются: логические функции, сумматор, схема сдвига, АЛУ (ALU, Arithmetic Logic Unit).

Полусумматор и полный сумматор

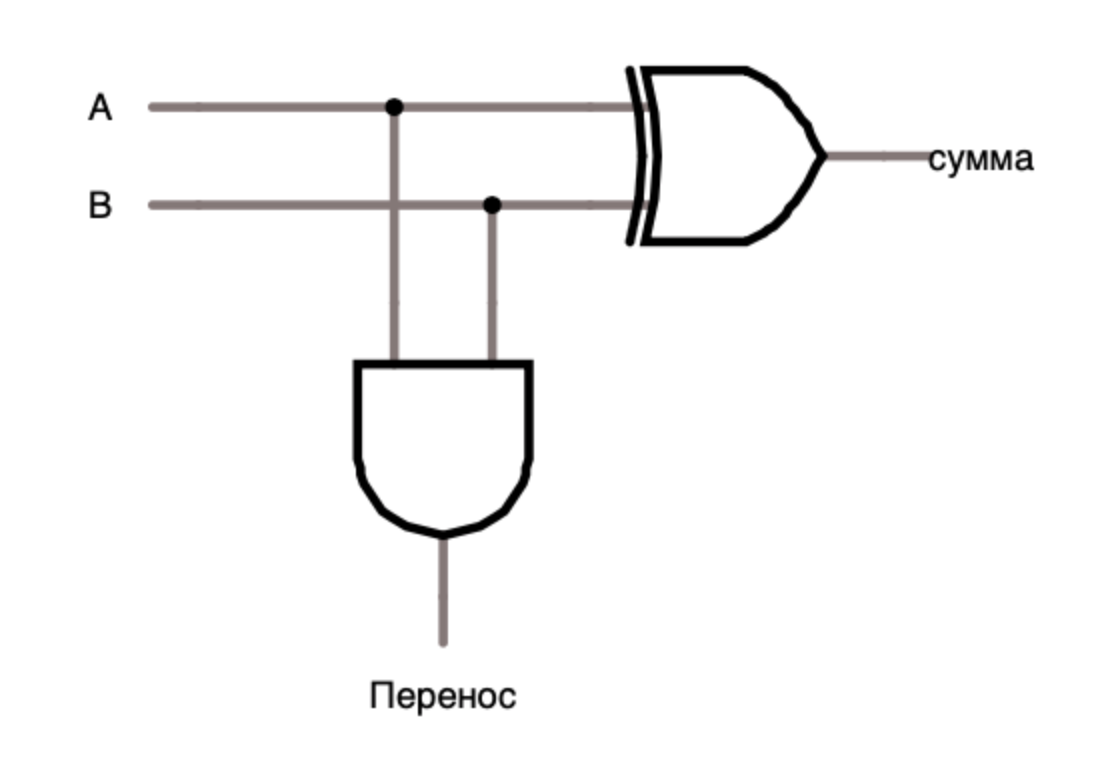

Полусумматор состоит из двух входных и двух выходных линий, Полусумматор является простой схемой (рис. 1.6) из двух вентилей: И и ИСКЛЮЧАЮЩЕЕ ИЛИ. Сам по себе полусумматор может складывать только одноразрядные значения, но зачем же тогда нам нужен полный сумматор? В основном мы хотим складывать значения с большей разрядностью, но только одним полусумматором мы удовлетворить это желание не может. Когда мы складываем два одноразрядных значения, то у нас может произойти переполнение (табл. 1.3 последняя строка истинности в столбике перенос). Это когда результат операции не помещается в той разрядности, которой обладают входные элементы (в данном случае 1). При сложении двух единиц получает двойка, которую нельзя сохранить в одном бите, поэтому необходимо перенести его, чтобы воспользоваться при дальнейших вычислениях, но так как в полусумматоре не предусмотрена возможность использования двух значений и переноса одновременно, то складывать значения с разрядность более чем единица не получится. Например, допустим мы складываем два 3-разрядных числа, 5 (101 в двоичной) и 7 (111 в двоичной), сложение двух чисел начинает с младших разрядов, на входы полусумматора направляются 1 и 1, на выходе суммы получаем 0 и на выходе переноса 1, вот здесь и возникает проблема, следующими значениями, которые должны пойти в полусумматор это 0 и 1 соответственно, но, что делать с переносом, ведь для него нет никакого свободного входа, а отбросить его нельзя, поэтому полусумматоры не могут напрямую использоваться для сложений.

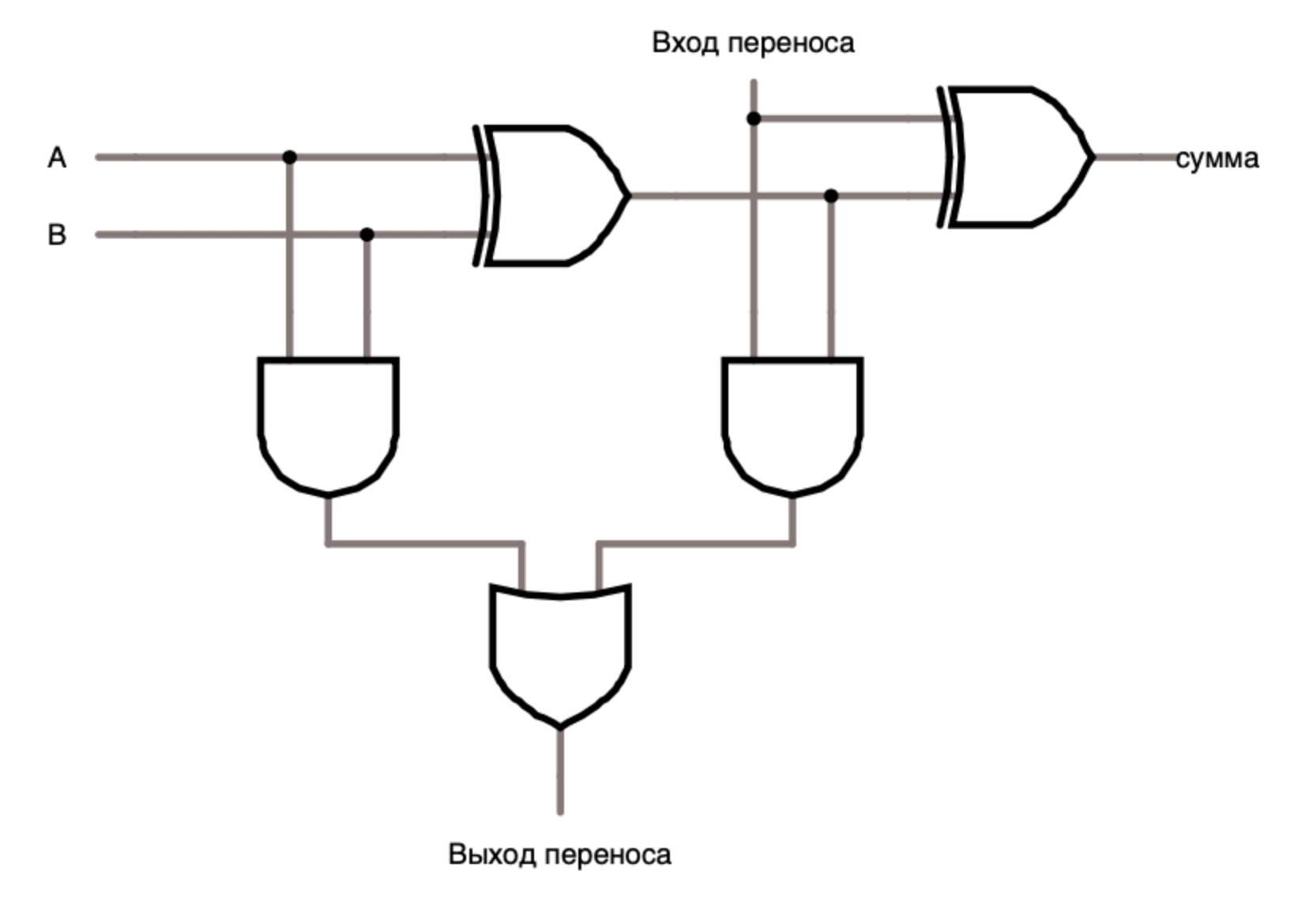

У полного сумматора есть (рис. 1.7) три входных линии и две выходные линии. Входной перенос, как и выходной, используется для возможности объединения сумматоров в один с большей разрядностью. Сумматор состоит из двух полусумматоров, чтобы построить сумматор большей разрядности, необходимо только объединить сумматоры через входные и выходные переносы.

Рисунок 1.6. Схема полусумматор.

Таблица 1.3. Таблица истинности полусумматора.

| A | B | Сумма | Перенос |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Рисунок 1.7. Схема полного сумматора.

Таблица 1.4. Таблица истинности полного сумматора.

| A | B | Вход перенос | Сумма | Выход перенос |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Схема сдвига

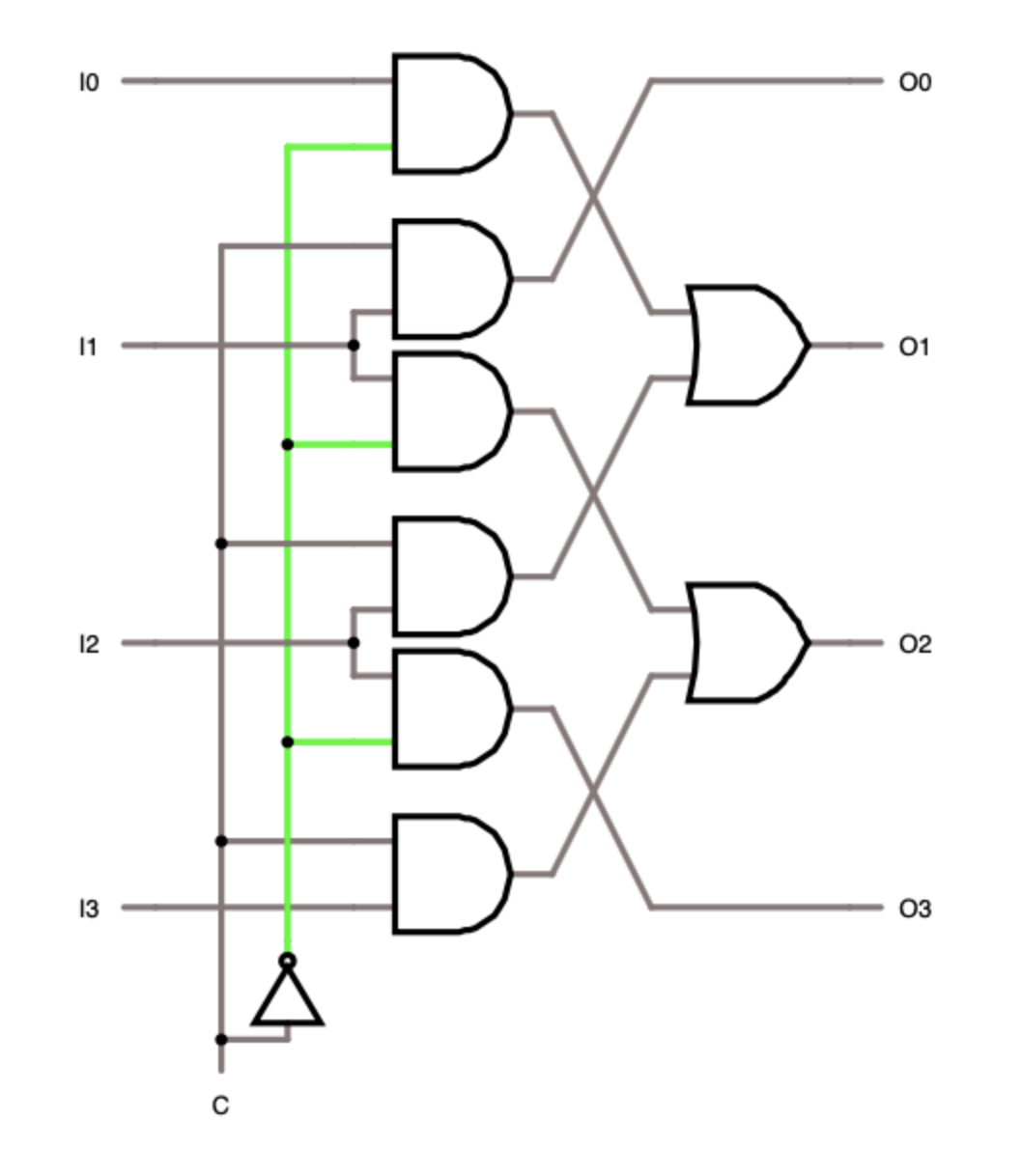

Сдвиг необходим для того, чтобы, например, выполнять умножение (сдвиг влево) и деление (сдвиг вправо), но только с числами, которые являются степенью двойки (1, 2, 4, 8 и тд). Схема сдвига (рис. 1.8) должна выполнять смещение на одну позицию влево или вправо в зависимости от бита направления. Бит направления (С) в зависимости от своего значения включает те или иные вентили И. Если он равен 0 (сдвиг влево), то сигнал который идет напрямую (то есть не проходит через НЕ) будет выключать вентиль который находятся выше в паре из двух вентилей И и один крайний вентиль И снизу. Сигнал, который проходит через НЕ, будет включать нижние вентиль в паре из двух вентилей И и один крайний вентиль И сверху. Это значит, что входные значения In будут выходить только из вентилей И выходные сигналы, которых направлены в нижнюю сторону; старший бит (I3) будет утерян, так как самый нижний вентиль И не пропустит входной сигнал дальше. Аналогичная ситуация происходит, когда бит направления равен 1 (сдвиг вправо), только теперь будут включены другие вентили И и сигнал уже будет направлен в противоположную (в данной реализации) сторону, и, следовательно, произойдет сдвиг вправо.

Рисунок 1.8. Схема сдвига.

Арифметико Логическое Устройство

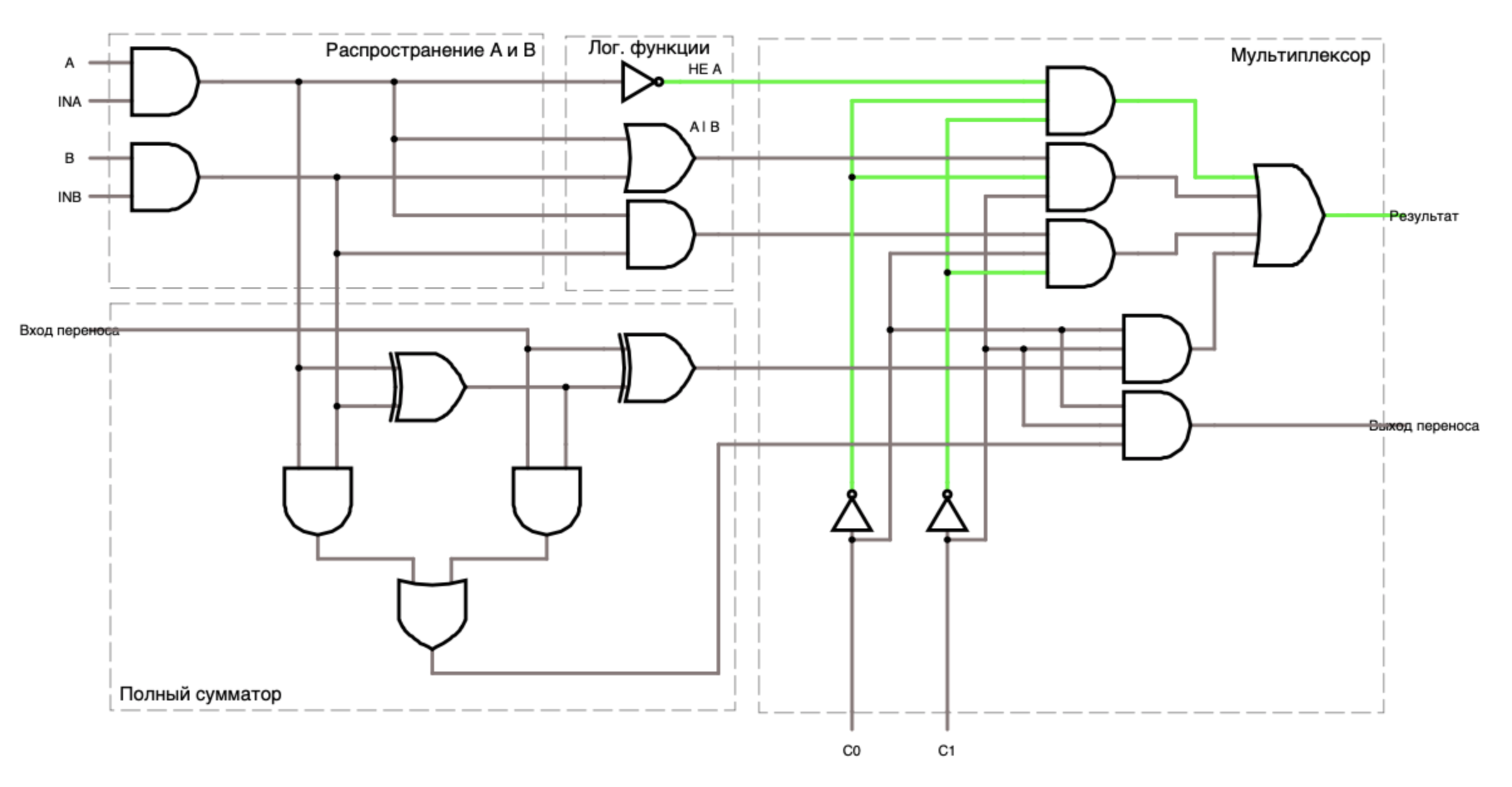

АЛУ — это схема (рис. 1.9), которая содержит в себе множество арифметических схем, она предназначена для того, чтобы в одном месте хранить все операции необходимые для какой-либо цели. Реализация АЛУ разделяется на несколько частей (в данной реализации): распространение входных операндов, логические функции, сумматор и мультиплексор. Как мы помним декодер должен выполнять«включение» операций, но здесь я решил сделать мультиплексор, который подает на выход «Результат» значение, только одной из четырех операций; два нижних вентиля И в нем делят одну и ту же комбинацию при которой мультиплексор работает, это необходимо потому, что «Выход переноса» и «Сумма» сумматора являются частью одной операции, то есть оба этих входа должны работать только когда выбрано суммирование. Наш АЛУ предназначен для работы с одноразрядными значениями, но его можно почти без проблем изменить на большую разрядность. Входные линии INA и INB предназначены для включения/выключения A и B соответственно.

Рисунок 1.9. Схема АЛУ.

Интегральные схемы

Также известна как микросхема, эта те же схемы показанные выше, только они помещена в корпус, который определяет, то где должны находится выводы для сигналов. Этот вид схем возник из-за того, что продавать отдельные схемы и вентили не очень целесообразно: по крайне мере из-за того, что нет стандарта, который бы говорит как, где и в каком кол-ве должны располагаться входные и выходные сигналы.

Есть куча разных видов корпусов, но мы рассмотрим наиболее известные:

- Dual Inline Package (DIP) представляет собой корпус (рис. 2.0а) у которого выводы (входные и выходные сигналы) расположены с двух сторон параллельных друг другу, кол-во выводов в данном корпусе варьируется в пределах от 14 до 68 (только четное кол-во). Данный корпус используется при небольших и/или дешевых схемах.

- Pin Grid Array (PGA) обладает выводами со всех четырех сторон (рис. 2.0б).

- Land Grid Array (LGA) обладает выводами в виде контактов по всей (зависит от стандарта) площадки (нижняя часть) корпуса. LGA (рис. 2.0в) обладает одним важным преимуществом перед другими корпусами: большое кол-во выводов, что особенно важно для таких микросхем как процессоры. Замечу, что процессор не то же, что и CPU, процессоры это, любая микросхема, которая производит вычисления, CPU же состоит из микроархитектуры, в частности АЛУ и блока управления (control block).

Рисунок 2.0a, б, в. Виды корпусов.