Почему процессоры Apple M1 такие быстрые

В конце 2020 года Apple выпустили первую линейку ноутбуков на собственном процессоре M1. Это было большое событие, потому что:

- Процессоры Intel к этому моменту морально устарели.

- В линейке ноутбуков Apple не было ничего нового уже года два.

- Первые тесты показали, что компьютеры на M1 очень быстрые и энергоэффективные.

Давайте разберёмся, в чём магия процессора M1 и стоит ли сейчас рассматривать его как рабочий инструмент. Стоит ли переходить на ноутбуки с процессорами Apple сейчас или в ближайшее время?

Эта статья — разбор видеоролика, который вышел на канале Engadget. Если знаете английский, лучше посмотрите видео, а если нет — читайте нашу короткую версию.

Процессоры CISC и RISC

— CPU с RISC-архитектурой (RISC — reduced instruction set computer — компьютер с сокращенным набором команд).

CPU первого типа являются традиционными, а их система команд включает большое количество команд для выполнения арифметических и логических операций, команд управления, пересылки и ввода-вывода данных. При считывании из операнда кода операции процессор обращается в ПЗУ микрокоманд и получает набор микроинструкций, реализующий алгоритм выполнения данной команды.

Такие CPU способны реализовывать любой алгоритм, который предварительно кодируется в системе команд данного CPU. Большинство универсальных CPU аппаратно поддерживают только целочисленную арифметику. Арифметика же с плавающей точкой реализуется программно во внутренних сопроцессорах. Сопроцессор расширяет набор команд ЭВМ. Когда основной процессор получает команду, которая не входит в его рабочий набор, он передает управление сопроцессору с целью ее выполнения.

Формально к этому классу относятся в большей или меньшей степени все нынешние Athlon, Pentium и прочие процессоры для IBM PC-совместимых компьютеров. В большей или меньшей потому, что те или иные заимствования идей и методов RISC имеются практически в каждом современном чипе.

Из названия RISC следует, что основу архитектуры составляет сокращенный набор команд. Сокращенный — в данном контексте означает также упрощенный для достижения максимальной производительности. Команды в архитектуре RISC имеют фиксированную и небольшую длину, они не нуждаются в интерпретации. С другой стороны, RISC-процессоры обладают значительным числом регистров, что позволяет хранить большое число данных на кристалле процессора и упрощает работу компилятора по распределению переменных по регистрам. Использование трехадресных команд упрощает их дешифрацию и дает возможность сохранять большее число переменных в регистрах без перезагрузки.

По мере развития архитектуры RISC появлялись все новые возможности наращивания производительности. Ключевыми из них являются суперскалярная (многоконвейерная) обработка, внеочередное выполнение команд, появление смешанных или групповых команд для выполнения часто повторяющихся последовательностей. Однако RISC-процессоры не являются суперскалярными в полном смысле слова, и реализация параллельных вычислений в рамках этой архитектуры достаточно сильно ограничена.

Еще одним фактором, сдерживающим стремительный рост производительности процессоров на основе архитектуры RISC, является проблема условных переходов. Проблема характерна для любой архитектуры, поскольку условные переходы значительно тормозят работу процессора. Однако бороться с ними в случае архитектуры RISC особенно сложно, ввиду ограниченного набора инструкций – меньшее число команд ведет к росту числа ветвлений.

Основные задачи распараллеливания вычислений (ILP — Instruction Level Parallelism):

— проверка зависимостей между инструкциями для выявления тех из них, которые можно сгруппировать для параллельного выполнения;

— распределение инструкций между функциональными блоками процессора;

— определение момента начала выполнения инструкций.

На основе статистического анализа кода множества CISC-приложений определяются наиболее часто используемые команды; уменьшение же числа команд позволяет увеличить число внутренних регистров (пересылка между регистрами выполняется быстрее всего), сделать конвейер более эффективным и поднять частоту его работы (чем более простые команды в нем исполняются, тем выше частота). Несмотря на значительно увеличившийся объем программного кода, RISC-процессор будет работать в несколько раз быстрее CISC-процессора с одинаковой частотой: специализация всегда предпочтительнее универсальности в плане быстродействия.

Разницу между RISC- и CISC-программами можно пояснить на простом примере. Но для начала оговорим некоторые детали: память компьютера адресуется по номеру строки и столбца, из которого осуществляется выборка (или в который производится запись). Операции над значениями из памяти производятся в исполнительном блоке, который, однако, может работать лишь с данными, загруженными в процессорные регистры.

Пусть нам нужно умножить два значения в памяти по некоторым адресам 2:2 (строка:столбец) и 5:4. CISC нацелен на исполнение задачи при минимуме команд: набор инструкций процессора строится таким образом, чтобы все более или менее сложные действия решались одной командой. Предположим, что в CISC- процессоре имеется команда MULT, которая выбирает указанные значения из ячеек памяти, записывает их в различные регистры и сохраняет результат в соответствующем регистре. Тогда задача умножения решится в одну строку кода:

MULT 2:2, 5:4

RISC-процессоры используют простые инструкции, которые исполняются за один такт. В этом случае вместо MULT потребуются команды LOAD/STORE, загружающие данные из памяти в регистр и записывающие их обратно, а также команда PROD, выполняющая умножение данных в двух некоторых регистрах. Эквивалентом MULT для RISC-процессора будет следующий код:

LOAD A, 2:2

LOAD B, 5:4

PROD A, B

STORE 2:3, A

Очевидно, код длиннее, но скорость выполнения операций на регистрах в 4 – 8 раз выше.

Таблица 1. Различия CISC и RISC

| CISC | RISC |

| Акцент на железо | Акцент на софт |

| Включает многотактовые сложные инструкции | Сокращенный набор однотактовых инструкций |

| Принцип «память-память» — работа с регистрами осуществляется автоматически | Принцип «регистр-регистр» — отдельные инструкции для передачи данных «регистр память» |

| Небольшой размер кода, много циклов в секунду | Мало циклов в секунду, большой размер кода |

| Транзисторное пространство используется под размещение сложных инструкций | Транзисторное пространство используется для увеличения количества регистров |

В принципе, с увеличением объема кода можно мириться, если этот увеличенный объем позволит в несколько раз повысить быстродействие – при необходимости программы пишут на ассемблере. Кроме того, RISC-код очень эффективно «распараллеливается».

В чем тогда причина непринятия RISC рынком IBM PC? Во-первых, наборы инструкций CISC и RISC несовместимы. CISC-кодов для PC-программ было написано очень много, а под RISC — на порядки меньше. Создавались эмуляторы, автоматически транслирующие CISC-инструкции в RISC (подобные приемы увеличения скорости обработки используются в современных CISC-процессорах), но работали они настолько медленно, что разница в производительности между настоящими и эмулированными CISC практически сводилась к нулю. Таким образом, эмулировать CISC на RISC-процессорах оказалось неэффективно, а главное — экономически нецелесообразно.

Во-вторых, как следствие сыграла свою роль несовместимость программного обеспечения. Для х86 уже были написаны DOS и набирающая популярность Windows, а различные RISC- процессоры базировались на Unix, причем, как правило, на несовместимых между собой ее версиях. Да и программ для них было куда меньше, особенно пользовательских. В-третьих, несмотря на кажущуюся «упрощенность», RISC-процессоры были дороги — они выпускались сравнительно небольшими партиями для высокопроизводительных рабочих станций, и производители не считали нужным ни экономить на материалах, ни оптимизировать дизайн, ни упрощать чипсет и материнскую плату.

В некоторых сферах (научные ресурсоемкие вычисления), действительно, конкурировать с RISC системам на базе CISC-процессоров было сложно, зато во всех остальных недорогие и достаточно производительные x86-процессоры остались вне конкуренции. Для создания конкуренции Intel в 1991 году Apple, IBM и Motorola основали альянс AIM Alliance, который занялся созданием дешевого, быстрого и современного RISC-процессора. В 1993 году была представлена спецификация платформы PowerPC, а также первый чип — 32-разрядный PowerPC 601, работавший на частотах 50 и 66 МГц.

Название PowerPC пошло от многочиповой RISC-архитектуры IBM POWER, на базе системы команд которой и был основан первый процессор. Чип рассеивал намного меньше тепла, чем его конкурент в лице Intel Pentium, и работал зачастую быстрее его. Вслед за 601 появились 603/604 модели, затем в 1997 — PowerPC 750 (G3) с L2-кэш и ускоренной системной шиной. В 1999 модельная линейка процессоров PowerPC пополнилась PowerPC 7400 (G4) — «конкурентом» Intel Pentium III, представившим поддержку набора команд для векторных вычислений AltiVec (также известного как VMX — Vector Multimedia eXtension — «мультимедийное расширение» PowerPC).

Однако с появлением и совершенствованием архитектуры Intel NetBurst (в Pentium IV) процессоры компании закрыли единственное слабое место, которое позволяло PowerPC выглядеть более выигрышно: заметно ускорив операции с плавающей точкой, х86- процессоры оказались самыми быстрыми и дешевыми на рынке. PowerPC-чипы же остались основой Apple Macintosh и различных встраиваемых систем (благодаря низкой рассеиваемой мощности) — системы на их базе, даже с учетом более дешевого процессора, все равно получались заметно дороже IBM PC совместимых компьютеров. Кардинальным образом ситуацию не изменил и выход нового процессора от IBM — PowerPC 970 (G5). Он позволил лишь приблизиться к x86 фаворитам в некоторых приложениях.

В настоящее время RISC-CPU широко применяются в проблемно-ориентированных компьютерах повышенной вычислительной мощности; очень часто – в мультипроцессорных системах.

Подавляющее большинство наших смартфонов работают на чипах, основанных на архитектуре Arm, тогда как архитектура x86 доминирует среди ноутбуков, десктопных компьютеров и серверного оборудования. Но в США, Европе и особенно в Азии быстрыми темпами растет число компаний, которые обращают внимание на процессорную архитектуру с открытым исходным кодом под названием RISC-V.

Открытость и бесплатность позволяет даже стартапам разрабатывать собственные чипы без дорогостоящих лицензионных сборов, необходимых для использования проприетарных архитектур. Например, если вы хотите создать собственный Arm-процессор, вам придется заплатить авансовый сбор от 1 до 10 миллионов долларов, а также выплачивать роялти в размере 0,5-2% с продаж. Очевидно, из-за этого производить Arm-чипы могут только достаточно крупные компании, а это в том числе тормозит их развитие.

Открытая архитектура RISC-V была разработана исследователями из Калифорнийского университета в Беркли и впервые показана широкой публике в 2010 года. Как и Arm, x86 и остальные процессорные архитектуры, RISC-V представляет собой ISA — архитектуру с набором команд, которые позволяют программистам и написанному ими программному обеспечению напрямую управлять компьютерным оборудованием.

Оцените легкость архитектуры: так, в базовом наборе RISC-V всего 11 арифметических инструкций, а для создания более-менее современной SoC их потребуется 39. Для сравнения, некогда простая архитектура Arm в текущей версии ARMv8 разрослась до 1000 инструкций, а x86 тут лучше вообще не упоминать.

Благодаря гибкости открытого исходного кода RISC-V становится все более популярной архитектурой для создания чипов в таких компаниях, как Seagate и Western Digital Corp., занимающихся созданием больших кластеров для хранения данных. Интересуется такими чипами и китайский гигант электронной коммерции Alibaba, и даже правительственные организации, такие как DARPA (Управление перспективных исследовательских проектов Министерства обороны США).

Одна из первых плат с 28-нм RISC-V процессором Raven1, показанная в июне 2012 года.

Но почему возник такой большой интерес к RISC-V? Во-первых, изначально небольшой набор инструкций позволяет идеально заточить софт под «железо», тем самым повысив энергоэффективность и производительность чипов. Во-вторых, архитектура модульная — можно легко создать SoC из разных процессорных ядер с разными наборами инструкций. В-третьих, открытость позволяет сэкономить на разработке ОС, компиляторов и драйверов, так как в репозитариях уже хватает качественного и доступного всем бесплатно кода.

Также отмечается полная обратная совместимость: старый софт будет без проблем работать на новом «железе», так как базовый набор команд стандартизован. Ну и куда в современном мире без безопасности: открытость архитектуры резко усложняет создание «закладок».

Поэтому не удивительно, что эта архитектура активно развивается. Так, Nvidia уже использует RISC-V в своих графических процессорах Ampere (RTX 3000) — даже с учетом того, что компания планирует приобрести Arm Holdings, владельца архитектуры Arm. Intel также может помочь ускорить внедрение RISC-V за счет расширения своего бизнеса по производству кремниевых чипов, нацеленного в том числе и на создание CPU и SoC на этой открытой архитектуре.

Еще одним признанием RISC-V можно назвать перемены в компании Wave Computing, которая владеет архитектурой MIPS — на ней работает немало бытовых приборов и даже консолей, таких как PSP или PlayStation 2. Однако теперь компания отказывается от своей архитектуры и озвучила новые планы по разработке чипов на базе RISC-V.

Ну и под конец нельзя забывать Азиатско-Тихоокеанский регион, который традиционно силен в создании процессоров и систем на кристалле. Число компании в нем, разрабатывающих свои решения на RISC-V, постоянно растет, поскольку такие страны, как Индия и Пакистан, уже приняли RISC-V в качестве своей национальной архитектуры для разработки собственных чипов.

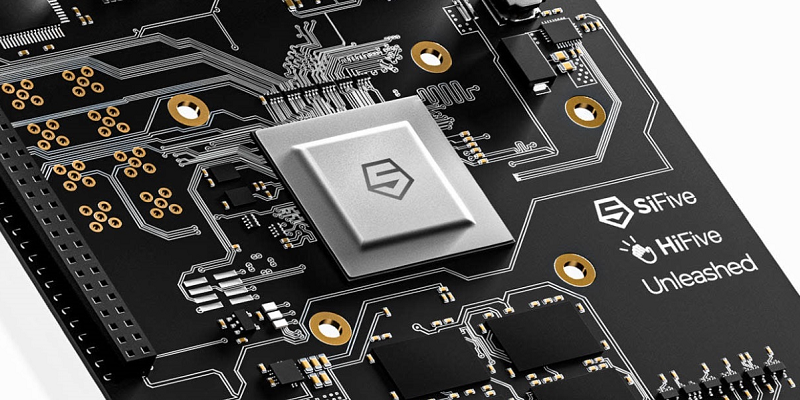

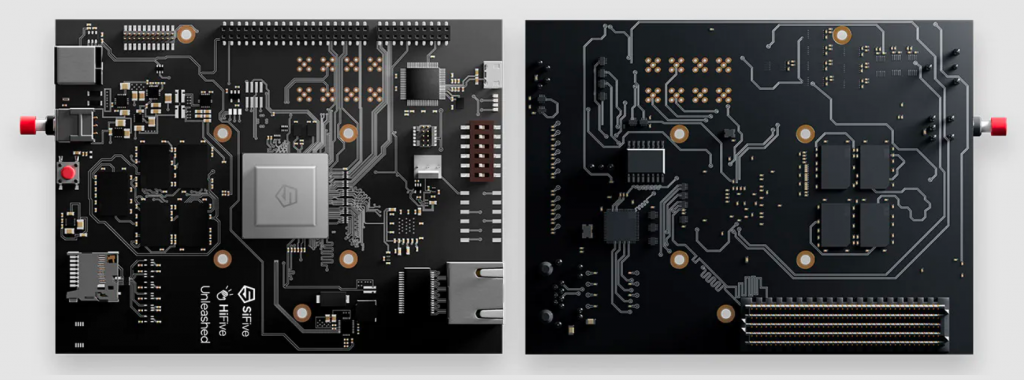

Одноплатный ПК HiFive Unleashed с 4-ядерным 1.5-ГГц RISC-V процессором U540 и 8 ГБ DDR4.

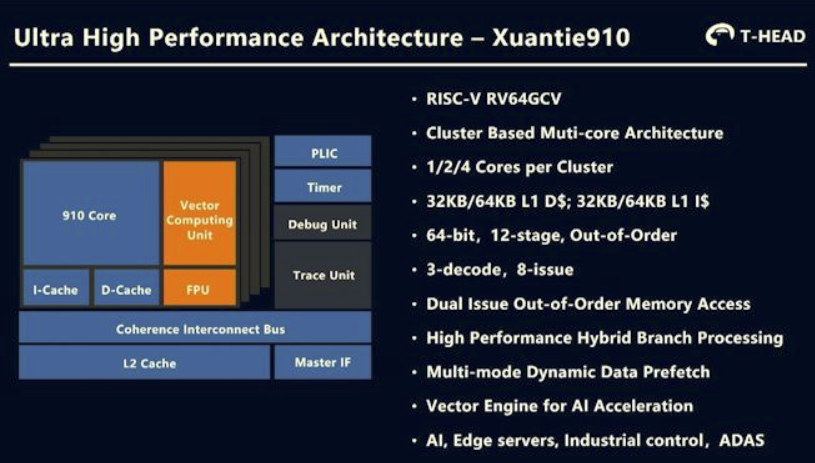

Китай также выделился как крупный приверженец RISC-V, несмотря на то, что большинство китайских технологических компаний по-прежнему в значительной степени полагаются на архитектуры Arm и x86. Так, в 2019 году холдинг Alibaba сообщил, что его дочерняя компания Pingtou Ge разработала процессор XuanTie 910 на основе архитектуры RISC-V. Он имеет 16 ядер, базируется на 12-нм техпроцессе и ощутимо быстрее конкурентов по производительности на герц, что делает его хорошим выбором для использования в продвинутой «умной» технике.

Также высказываются предположения о том, что предстоящее приобретение Nvidia компании Arm за 40 миллиардов долларов может осложнить дальнейшее использование одноименной архитектуры китайскими компаниями из-за экспортных санкций США. Эта неопределенность также может заставить крупные китайские компании искать «запасной аэродром», и RISC-V отлично подходит на эту роль. Но Arm, похоже, в любом случае стремится удержать своих китайских клиентов: их новая архитектура ARMv9 на данный момент свободна от санкций Соединенных Штатов, что позволяет ее использовать, например, компании Huawei.

В любом случае, архитектура Arm сейчас твердо стоит на ногах: она имеет поддержку в лице Apple, занимает 95% рынка смартфонов и каждый третий чип в мире базируется именно на ней. Конечно, компания Arm знает о появлении сильного конкурента в лице RISC-V, и даже пыталась воспрепятствовать его развитию маркетинговым путем: в 2018 году она открыла сайт (который сейчас уже не работает), где подчеркивала преимущества ARM-архитектуры по стоимости чипов, уже созданной экосистеме, большей безопасности и фрагментации. Впрочем, раз сайт закрылся — значит, маркетинговое давление успеха не возымело.

Тем не менее, компания ARM указывает на некоторые возможные проблемы с RISC-V, когда дело доходит до проверки и поддержки архитектуры с открытым исходным кодом при широком коммерческом внедрении в массовые чипы. «Риск заключается в том, что экономия средств, связанная с лицензированием, часто сводится к минимуму за счет времени и денег, которые тратятся на проверку, физическое проектирование и разработку программного обеспечения для устройств с минимальной дифференциацией или без нее», — говорит Мохамед Авад, вице-президент бизнес-отдела компании Arm по разработке устройств интернета вещей.

RISC-V International, похоже, осознает эти проблемы. В настоящее время в организации работают десятки технических рабочих групп, которые следят за тем, чтобы архитектура соответствовала различным стандартам, обеспечивала надежную защиту и имела максимальную гибкость для применения в большинстве задач.

Несмотря на разные подходы, и RISC-V International, и Arm, похоже, согласны с тем, что будущее разработки чипов будет тесно связано с разнообразным набором архитектур. По мнению Авада, открытый исходный код будет играть немалую роль в разработке микросхем будущего наряду с традиционными моделями лицензирования и инструментами автоматизации проектирования.

Точно так же Марк Химельштейн, технический директор RISC-V International, видит «множество мест для сосуществования нескольких процессорных архитектур в мире», даже когда он указывает на модель RISC-V с открытым исходным кодом и отсутствием лицензий как на конкурентные преимущества этой архитектуры.

«Мы все чаще видим, что люди хотят самостоятельно контролировать свою судьбу», — говорит Химельштейн. «Это то, чему их научил Linux, и это то, чего они хотят и от оборудования».

Компьютеры на базе risc процессора

RISC (англ. reduced instruction set computer 1 2 — компьютер с сокращенным набором команд) — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. В системах команд первых RISC-процессоров даже отсутствовали команды умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).

План SiFive по компьютерам на базе Linux и RISC-V

Компания SiFive показала план по компьютерам на базе Linux и RISC-V на базе процессора SiFive FU740 SoC. Этот пятиядерный процессор состоит из четырех SiFive U74 и одного SiFive S7 core. Компьютер ориентирован на разработчиков и энтузиастов, которые хотят строить системы на базе архитектура RISC-V и предполагается не как конечное решение, а как база для чего-то большего. На плате будут 8GB DDR4 RAM, 32GB QSPI flash, microSD, порт консоли для отдладки, PCIe Gen 3 x8 для графики, FPGA или других устройств, M.2 для накопителя NVME (PCIe Gen 3 x4) и Wi-Fi/Bluetooth (PCIe Gen 3 x1), четыре USB 3.2 Gen 1 type-A, Gigabit Ethernet. Цена предполагается в $665, доступность в четвертом квартале 2020го.

Не взлетит. Нужно, но не взлетит. ☹

Я, кстати, читал про нее на официальном сайте. Интересно, сколько оно стоит.

Цена предполагается в $665, доступность в четвертом квартале 2020го

или на базе архитектОра ?

Считай это чутьём. А оно меня ещё не подводило.

Не окупится оно.

В SiFive сейчас работает Кит Паккард (Keith Packard) из Xorg. В подразделении свободного ПО.

расскажите чем лучше/хуже ARM, x86_64, кроме свободности.

Исправляйте дальше. КАК в новости на 5 строк текста, где половина — англоязычные сокращения, можно 3 раза исправления делать. Таланты, однако.

Можно заказать свой процессор с нужными параметрами. Эта плата для создания и отладки ПО под архитектуру сделана.

Я вот что не понимаю, раз на плате полноценный pcie и atx колодка, то зачем припаяли память?

Потому что надо с бюджетного сегмента начинать. Чтобы ненакладная игрушка была. А уж когда окажется, что оно немало может…

Возможно, чтобы отладку производить было легче. А то позапихивают какой-то FB-DIMM в колодку для DDR4, а потом мозги техподдержке сношают.

А так всё у всех одинаково.

как ты на игрушке будешь портировать драйверы устройств, это тебе не ARM.

Оно может JEDEC не умеет?

какие драйверы портировать и зачем, они и так должны работать

Famous last words

Должны, а может и не должны. Багрепортов с неработой драйверов на других архитектурах вагоны, там мелочи, но фиксить надо.

Не талант. Просто Шаман.

Ну да, ага. Учитывая, что на ppc64 не работает amdgpu…

расскажите чем лучше/хуже ARM, x86_64, кроме свободности.

Для юзера ничем, процессор аналогичен ARM или MIPS, отличий, ни программных, ни электрических не заметишь, если только не пишешь на ассемблере или ковыряешься в ядре OS на предмет прерываний или ещё какой сильно низкоуровневой хрени. Но и эти отличия не делают его ни лучше, ни хуже ARM или MIPS.

От x86 RISC-V отличается настолько же, насколько и ARM/MIPS. Ужор ядра на мегагерц меньше, команд на произведение каких-либо вычислений в среднем нужно чуть больше.

Да даже свободность RISC-V для конечного юзера готового процессора вообще никак не проявляется, потому что юзер не может поменять что-то в готовом кристалле. Может быть, при очень массовом выпуске цена на RISC-V при прочих равных будет чуть ниже, за счёт отсутствия лицензионных отчислений, только и всего.

Плюшки от свободности RISC-V прямо сейчас конечный юзер некоего железа может получить только в том случае если это железо — FPGA в котором юзер реализовал RISC-V процессор. Юзеру не надо никому платить за IP и ограничений на распространение исходников процессора нет.

Так что нет, для массового юзера какой-либо реализации RISC-V в кремнии, RISC-V ничем не лучше и не хуже аналогичного ARM/MIPS.

Тут есть небольшая филосовская проблема: кому надо портировать драйвера подключаемых устройств, если нет дешёвой массовой платы, которую кто то мог бы купить?

процессор аналогичен ARM или MIPS, отличий, ни программных, ни электрических не заметишь

так можно про любой CPU сказать

Хорошо, что появляется железо, но $666 за devboard — пока многовато для широкой публики. Жду дешёвых китайских SoC с нетерпением.

Соглашусь. Типа малинки что-то

Эта конкретная плата явно не рассчитана на массовость, а вот микроконтроллеры на RISC-V уже многие клепают. Надеюсь, скоро китайцы осилят и полноценные SoC, тогда массовые компьютеры на этой архитектуре станут реальностью.

Потому что надо с бюджетного сегмента начинать. Чтобы ненакладная игрушка была.

так не бывает в принципе — никакого бюджетного сегмента у нового процессора нет — надо как-то окупать затраты на несерийное производство